# Superconducting Optoelectronic Circuits for Neuromorphic Computing

Jeffrey M. Shainline,\* Sonia M. Buckley, Richard P. Mirin, and Sae Woo Nam National Institute of Standards and Technology, 325 Broadway, Boulder 80305, Colorado, USA (Received 30 September 2016; revised manuscript received 9 February 2017; published 23 March 2017)

Neural networks have proven effective for solving many difficult computational problems, yet implementing complex neural networks in software is computationally expensive. To explore the limits of information processing, it is necessary to implement new hardware platforms with large numbers of neurons, each with a large number of connections to other neurons. Here we propose a hybrid semiconductor-superconductor hardware platform for the implementation of neural networks and large-scale neuromorphic computing. The platform combines semiconducting few-photon light-emitting diodes with superconducting-nanowire single-photon detectors to behave as spiking neurons. These processing units are connected via a network of optical waveguides, and variable weights of connection can be implemented using several approaches. The use of light as a signaling mechanism overcomes fanout and parasitic constraints on electrical signals while simultaneously introducing physical degrees of freedom which can be employed for computation. The use of supercurrents achieves the low power density (1 mW/cm² at 20-MHz firing rate) necessary to scale to systems with enormous entropy. Estimates comparing the proposed hardware platform to a human brain show that with the same number of neurons (10<sup>11</sup>) and 700 independent connections per neuron, the hardware presented here may achieve an order of magnitude improvement in synaptic events per second per watt.

DOI: 10.1103/PhysRevApplied.7.034013

### I. INTRODUCTION

Many foundational concepts in information theory and computing were developed beginning in the 1930s and 1940s through the work of Turing [1], von Neumann [2], Shannon [3], and others. Given the variety of proposed approaches to computing, it is somewhat surprising that the current landscape of computing technologies exclusively uses the von Neumann architecture. There has long been an interest in the relationship between information, computation, and cognition [4,5]. Computing architectures drawing inspiration from biological neural systems have been considered for decades [6], but investigation of novel architectures is only now becoming urgent as we reach the end of Moore's law scaling. The recent surge in deep learning and neural networks marked by advances in hardware [7–9], applications [10], and theory [11–13] has increased our understanding of the importance of such systems for solving complex problems.

Lin and Tegmark have recently argued [13] that the physics of our Universe is conducive to representation by neural networks. While there is an infinite number of possible functions a network may try to approximate, only a very limited subset will be of interest in our physical world. Additionally, it has been shown mathematically [11,12] that the ability of a neural network to accurately represent different kinds of functions (the expressivity of the network) scales as  $k^{mn}$ , where m is the dimension of the

input, n is the number of hidden layers, and k is the number of nodes in each layer. This insight informs us that we can improve a network's ability to represent a broad range of functions both by increasing its width (k) and depth (n). Further, since the total information capacity of a computing system is proportional to the entropy, which scales with the number of distinct states which can be addressed by the system [14], computing systems based on complex interconnected networks, such as biological neural systems, offer extraordinary computational power.

To further maximize the information-processing capacity of such a system, it is desirable to fully utilize the time domain. For resilience to noise as well as temporally encoded information [15,16], signal communication via pulses, or spikes, is most advantageous, and such spike-encoded information is most powerful when many connections are established between processing units [16]. All of these findings taken together inform us that to implement neural networks most effectively in hardware, we should develop systems with a large total number of processing units, a large number of connections between units, and pulse-based communication.

Much like the von Neumann architecture has dominated modern computing, the hardware of silicon microelectronics has been similarly preeminent. It is possible that the ideal hardware platform for the next generation of computer architectures will also look very different. We make two conjectures which lead us to the hardware platform presented here. The first is that photons, based on their

<sup>\*</sup>ieffrey.shainline@nist.gov

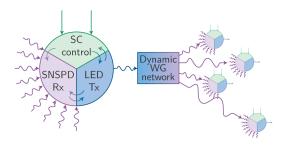

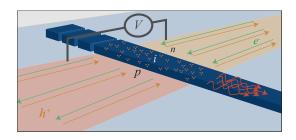

FIG. 1. Schematic representation of the proposed device concept. SC, superconducting; SNSPD, superconductingnanowire single-photon detector; Rx, receive; Tx, transmit; WG waveguide.

noninteracting bosonic nature, will prove advantageous over electrons for achieving spike-based communication over networks with a large number of connections between nodes. That is to say, photonic fanout will overcome limitations of electronic fanout. The second conjecture is that superconducting circuits will enable lower power densities than semiconducting circuits, thereby leading to systems with a larger number of processing units and greater total complexity. In conceiving of a hardware platform integrating photonic with superconducting devices, we find a feasible route to highly scaled, multiphysical systems with extraordinary potential for computing complexity and experiments in information physics. A schematic representation of the concept is shown in Fig. 1.

The optoelectronic hardware platform is based on waveguide-integrated semiconductor light emitters working with superconducting detectors and electronics to implement weighted, directed networks [17]. Optical signals between neurons are communicated through reconfigurable nanophotonic waveguides. Utilization of light-emitting semiconductors allows efficient access to photonic degrees of freedom (frequency, polarization, mode index, intensity, statistics, and coherence), which achieve complex functionality analogous to chemical signaling in biological organisms and possibly with information-processing capabilities far beyond. Light enables massive interconnectivity with no need for time-multiplexing schemes that can limit the event rates of complementary metal-oxide-semiconductor (CMOS) systems [9,18]. Photonic signals are received and integrated by superconducting single-photon detectors. Firing thresholds and gain are controlled by a dynamic superconducting network, and neuron-generated photonic signals can reconfigure this current-distribution network. By employing superconducting electronics, we can approach zero static power dissipation [19], extraordinary device efficiencies, and utilize Josephson-junction circuits including single-flux-quantum devices [20–22].

Within this hardware platform, memory can be implemented via several means. These include temporally fixed synapses achieved with branching waveguides, synaptic weight variation via the actuation of locally suspended waveguides or through the use of magnetic Josephson

junctions [23], or other magnetic and flux-storage components. The suspended waveguides that we explore in more detail in this work are reconfigurable on a time scale of  $1 \mu s$ . None of these approaches draw power in the steady state.

The combination of efficient faint-light sources and superconducting-nanowire single-photon detectors interacting in an integrated-photonics environment enables neuronal operation with excellent energy efficiency, enormous intra- and interchip communication bandwidth, light-speed-limited latency, compact footprint, and relatively simple fabrication. The optoelectronic hardware platform is predicted to achieve 20 aJ/synapse event. By comparison, many CMOS systems are on the order of 20 pJ/synapse event [9,24,25], or in more recent work, hundreds of femtojoules per synapse event [26]. For these reasons, the proposed platform appears promising for advanced neuromorphic computing at the highest level of performance, while the compact nature and roomtemperature operation of CMOS circuits will inevitably remain better suited for a wide range of neuromorphic applications.

The article is organized as follows. In Sec. II, we present the foundational neuronal optoelectronic circuits and consider each of the requisite constituent components. In Sec. III, we discuss the coupling of these circuits as well as mechanisms for reconfigurable memory enabling plasticity and learning. In Sec. IV, we discuss concrete applications of this hardware platform and consider the spatial and power scaling. We conclude with Sec. V. Details of the device design are presented in the appendixes.

# II. OPTOELECTRONIC NEURONAL CIRCUITS

Information in neural systems is often referred to as "spike encoded," as interconnected neurons transmit information to one another in pulses [27]. An individual neuron (also referred to as a "processing unit," or simply, "unit") receives pulses from a number of upstream neurons. The neuron's input-output relation will be nonlinear, and if the integrated upstream signals exceed a certain threshold, the neuron may itself fire a pulse to its downstream connections. In this section, we describe superconducting optoelectronic circuits to emulate several biological neural responses. These circuits use integrated light-emitting diodes (LEDs) as transmitters with optical detectors as receivers. We next discuss the requirements for detectors and LEDs for this platform, and we motivate our choice from current technologies. Based on these choices, the energy per firing event is calculated.

## A. Detector choice

A neuron that uses photonic signals requires both a source of photons and a photon detector. The choice of detector is critical to the design and analysis of the hardware platform. The central aim of this hardware platform is to achieve massive scaling to large numbers of interacting neurons. Therefore, simple waveguide integration, extreme energy efficiency, high yield, and small size are principal concerns. A review and comparison of single-photon detectors can be found in Ref. [28]. Of all existing detector options, only those based on superconductors allow single-photon detection in the infrared with zero static power dissipation and single-photon sensitivity to enable operation at the shot-noise limit. Because a system based on superconducting detectors will enable operation in this limit, it offers a useful platform to test the role of noise in learning and evolution of complex, dynamical systems.

There is an additional energy cost associated with cooling superconducting detectors to cryogenic temperatures necessary for operation. Therefore, an alternative is to move away from low-light levels and use integrated detectors such as Si [29-31], Si defect [32,33], Ge-on-Si [34–36], or III–V detectors, either bonded to Si [37] or on a fully III-V platform [38]. Such detectors have low signalto-noise ratio requiring operation with significantly higher optical powers than if superconducting detectors are employed. While it may be possible to develop neuromorphic technology based on many of these detectors, we choose for this article to focus on superconductingnanowire single-photon detectors (SNSPDs) due to the high efficiencies (>90%) [39] at wavelengths below the Si band gap, simple on-chip waveguide integration [40–46], compact size, and speed. While operation at cryogenic temperatures imparts a fixed energy cost, the energy cost per operation is significantly decreased by allowing integration with superconducting electronics. Therefore, cryogenic systems are of use in a subset of neuromorphic applications where the required system size is sufficiently large that the savings in chip power outweigh the cryocooling cost. Additionally, low-temperature operation allows the use of certain LED designs that are not possible at room temperature, as we discuss in Sec. II G.

# B. Integrate-and-fire circuit

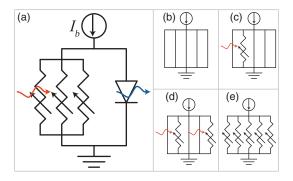

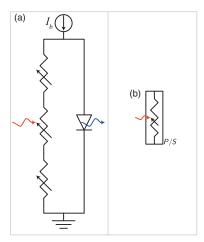

To encode information, the nodes of a neural network must have a nonlinear input-output relationship. In the proposed system, that nonlinearity is achieved via the transition of wires from the superconducting phase to the normal-metal phase. These phase transitions can be induced by absorption of a photon or by exceeding the critical current. A single SNSPD can be designed to fire with close to unity efficiency upon absorbing a single photon. We can think of this as an integrate-and-fire neuron in the limit of a single-photon threshold. In order to obtain an integrate-and-fire response with a threshold photon number larger than one, SNSPDs can be configured in parallel (step response) or series (continuous response). In Fig. 2(a), we show a circuit diagram of the parallel SNSPD

FIG. 2. (a) PND neuron circuit. (b) A PND with all wires superconducting. (c) A PND where one of the wires is driven normal by absorption of a single photon, redirecting the current through the other four. (d) A PND with two normal wires due to absorption of two photons. (e) A PND with all wires driven normal by exceeding the critical current. A LED in parallel with this PND now receives current, causing a firing event.

array referred to as a parallel nanowire detector (PND) [47,48]. One example of an integrate-and-fire circuit is accomplished by placing the PND in parallel with a LED. The thresholding mechanism is explained pictorially in Figs. 2(b)-2(e). In the steady state, the PND is superconducting and has zero resistance. The semiconducting LED has finite resistance, and, therefore, all current from the source  $I_b$  flows through the PND. When a sufficient number of nanowires in the PND has been driven to the normal state by the absorption of photons, the critical current of the array is exceeded, the array becomes resistive, and current is diverted to the LED. This diversion of current and the subsequent production of light via carrier recombination constitutes the firing event. The LED fires with a step response, meaning that the LED output is independent of the exact number of photons absorbed and depends only on whether or not the threshold is exceeded. The diversion of current to the LED allows the PND to return to the superconducting state. Once this occurs, current ceases to flow through the LED, the production of light stops, and the device is reset.

The minimum duration of a spike event is determined by the emitter lifetime. The integration time of the neuron can be engineered to be within the range of a few hundred picoseconds up to seconds. See Appendix A for a more detailed discussion of the temporal response of the circuits.

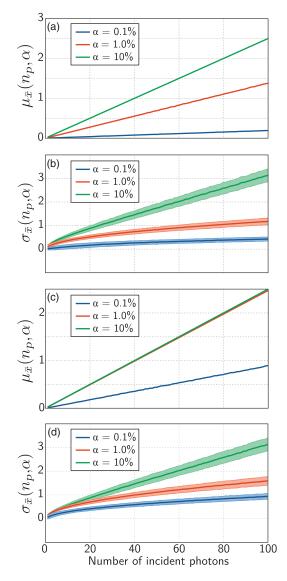

To model the spike probability of this circuit, we conduct Monte Carlo simulations of the device. The critical number of absorbed photons  $n_c$  is given by

$$n_c = N_{\text{NW}} - \frac{I_b}{i_c},\tag{1}$$

where  $N_{\rm NW}$  is the number of nanowires in the array,  $I_b$  is the bias current for the entire array, and  $i_c$  is the critical current of a single wire. Equation (1) is derived in Appendix B. Although each individual firing event

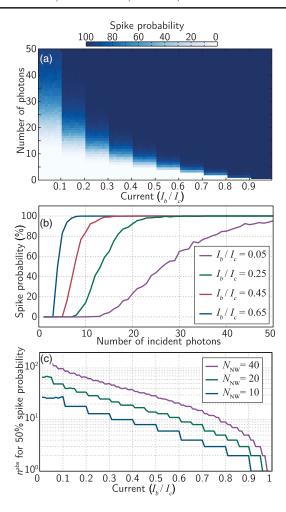

FIG. 3. Monte Carlo simulation of spike probability. (a) PND with ten SNSPDs. (b) The same simulation as (a) but with four traces isolated for clarity. (c) The number of absorbed photons which gives a 50% absorption probability plotted as a function of bias current. Traces for PNDs with 10, 20, and 40 nanowires are shown.

generates the same current pulse across the LED (i.e., a step response), a given number of input photons causes only the neuron to fire with some probability. This is due to the stochastic nature of the photon-absorption events, which we discuss in more detail in Appendix C. The results of these simulations are shown in Fig. 3. The probability of a spike occurring is plotted as a function of the number of photons incident on the device for various bias currents ranging from 0.01 of the array critical current  $(I_c)$  to 0.99  $I_c$ in steps of 0.01  $I_c$ . In Fig. 3(a), we show the behavior of an array with ten SNSPDs in parallel. Figure 3(b) shows the spike probability versus the number of incident photons for four values of bias current; these data are a subset of that shown in Fig. 3(a), plotted separately to illustrate the shape of the traces. The Monte Carlo simulations which produce these plots are conceptually based on the neuron design of Fig. 4 and proceed as follows. A given number of photons is assumed to be incident on a PND array. The pulse is assumed to pass each nanowire of the array in sequence. At

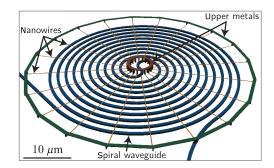

FIG. 4. The spiderweb neuron. The scale bar is shown for reference, but significantly more compact implementations of this device can be achieved.

each pass, a random number between zero and one is generated. If this random number is less than or equal to the assumed absorption probability (1% in these calculations), the number of photons in the pulse is reduced by one, and the state of that nanowire is set to nonsuperconducting. The photon pulse is allowed to pass each nanowire of the array 100 times. The number of photons in the pulse which cause Eq. (1) to be satisfied is recorded for each bias current. The result of 1000 such simulations is averaged to calculate the probability for spiking to occur.

In Figs. 3(a) and 3(b), we observe that by adjusting the bias current, we can adjust the shape of the firing function versus photon number. Yet, adjusting the bias current cannot tune the threshold with arbitrary accuracy. In Fig. 3(a), it is evident that the spike probability for a PND array with ten nanowires separates into ten bands. Therefore, to achieve higher-photon-number differentiation, more wires must be integrated. This point is illustrated in Fig. 3(c). Simulations similar to that of Fig. 3(a) are conducted for PND arrays with 20 and 40 nanowires, and the number of absorbed photons  $(n^{abs})$  for which the spike probability reaches 50% is plotted versus the bias current. This figure further illustrates that the resolution of the PND array is limited by the number of nanowires in the array, resulting in discrete steps in the number of photons required for a spike event as a function of bias current. Because  $n_c$ and  $N_{\text{NW}}$  in Eq. (1) are both integers, the floor of the ratio  $I_b/i_c$  is effectively taken, and the utility of the current for setting the threshold is discretized. For the case of  $N_{\rm NW} = 40$ , the steps become quite small, and the curve is approximately continuous.

The simple model of Fig. 3 reveals that the PND array can achieve a high dynamic range in that the threshold can be tuned broadly in hardware by changing the number of wires in the array (from a single nanowire up to potentially thousands) as well as actively during operation by changing the bias current. The state space of the receiver, which scales as  $2^{N_{\text{NW}}}$ , can be made quite large in the regime where thousands of nanowires comprise the PND.

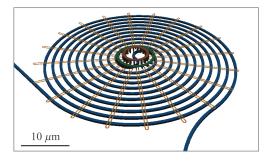

Figure 4 presents a neuron design well suited to a system with a few tens and possibly hundreds of connections. We

refer to this device as the spiderweb neuron. In this design, all upstream signals are combined on a single waveguide. This waveguide enters a spiral region in which it passes a number of SNSPDs which can be wired in series or parallel. Photon wave packets can pass several tens of SNSPDs several tens of times. The system can, thus, be engineered to spread the absorption probability evenly over the SNSPDs. In Fig. 3, the photons are assumed to pass each nanowire 100 times with a probability of absorption of 1% at each pass. The size of the detector portion of this neuron can be made as small as  $10 \times 10 \ \mu\text{m}^2$  and depends on the thresholding number of photons. For a threshold of 1000 photons, the device is approximately  $35 \times 35 \mu m^2$ . We discuss the model in more detail in Appendixes A and C, and other neuron designs are discussed in Sec. III A. In the calculations of Fig. 3, we assume all photons arrive in a short pulse, so nanowire rebiasing dynamics can be neglected. The complex dynamics of the PND receiver array in the case of arbitrary photon-arrival times is the subject of future investigation.

## C. Differentiable response circuit

In biological systems, the neuron response is not that of a step function but rather a nonlinear response taking the form of a sigmoid. For certain neural-network backpropagation algorithms, it is important that the response be continuous and differentiable [49]. Figure 5(a) shows the series-nanowire-detector (SND) [50] circuit which achieves a continuous and differentiable nonlinear response. In Fig. 5(b), we define a general optoelectronic circuit element symbolizing either the PND (Fig. 2) or the SND (Fig. 5). We envision the SND as a single length of superconducting wire with incident photons spread along the length of the wire. As in Fig. 2(a), the detector array is in parallel with the LED. When a single photon is absorbed by the SND, a

FIG. 5. (a) SND circuit. (b) Component diagram indicating either SND or PND array. This circuit symbol is used throughout this article.

length of normal wire called a hot spot emerges in series with the superconductor, leading to current redistribution between the two branches of the circuit. For common SNSPD materials, this resistance is approximately 1 k $\Omega$  for the typical wire width, while the length of the single hot spot is on the order of 100 nm [51,52]. As more photons are absorbed, more hot spots are created, and the resistance of the SNSPD increases. This resistance causes the voltage across the LED to increase, and sufficient current can be driven through the diode to produce an optical signal.

While attempts have been made to utilize this effect for number-resolving single-photon detection [50], we emphasize that we propose to utilize this circuit in a very different operating regime. To detect a single photon with near-unity efficiency, a SNSPD is driven close to its critical current, and the ensuing voltage pulse is measured across a  $50-\Omega$ resistor in parallel with the SNSPD. When a photon is absorbed, a 1-k $\Omega$  hot spot is produced, and nearly all current is diverted to the 50- $\Omega$  load. For the application at hand, the device is not intended to observe events of one or a few photons but rather hundreds to thousands. Thus, diverting the current through a high-impedance diode with I-V relationship approximated by Eq. (D1) enables thresholding with some dynamic range for higher numbers of absorbed photons. The model of this SND-based neuron considers simple joule heating behavior in that each photon-absorption event results in the same hot-spot resistance, when in reality, the hotspot resistance depends on the current through that branch of the circuit, which depends on the temporal dynamics of the preceding absorption events. A thorough study of these dynamics is the subject of future work.

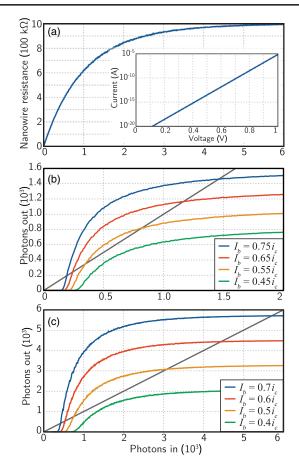

The electro-optic performance of the SND is analyzed in Fig. 6. The nanowire resistance as a function of the number of absorbed photons is shown in Fig. 6(a). In this model, we assume the photons are incident upon a length of out-andback nanowire [40–46] with 100-µm attenuation length, and it is assumed that two photons absorbed at the same location along the nanowire give rise to the same resistance as a single photon absorbed at that location. For this reason, the nanowire resistance levels off as a function of the number of absorbed photons. The current-voltage relationship of the LED is highly nonlinear, as shown in the inset, but above a certain number of absorbed photons, the entire length of the absorbing region of the superconductor is driven normal, and the absorption of additional photons results in no additional resistance, as shown in Fig. 6(b) and 6(c). Hence, the device has an input-output relationship with an exponential turn-on when a threshold number of photons is absorbed followed by a flattening of the output when the entire SND is driven normal. Figures 6(b) and 6(c) show the photon input-output relationship for two different nanowire designs with critical currents of 4 and  $8 \mu A$ , respectively, demonstrating the ability to tune the response in hardware. Note that the photon input-output

FIG. 6. Electrical characteristics for SND with  $l_{\rm wire}=100~\mu{\rm m}$ . (a) Resistance versus number of photons for the SND. Inset shows the exponential current-voltage curve for the LED. Photons out versus photons in for SNDs with (b)  $i_c=4~\mu{\rm A}$ ,  $\eta=1\%$  and (c)  $i_c=8~\mu{\rm A}$ ,  $\eta=0.1\%$ . Here,  $\eta$  is the efficiency of the LED.

relationship depends on the refractory period, as we discuss in Appendix A.

Based on the analysis of Fig. 6, in the SND-based neuron, the normal-state resistance of the SND and the applied bias determine the maximum voltage that can be achieved across the LED. This resistance and bias, in conjunction with the optoelectronic design of the LED, determines the number of photons generated, in contrast to the case of the PND where the number of photons generated is a step response determined by the bias current.

Both the PND-based integrate-and-fire circuit of Fig. 2(a) and the SND-based continuous-response circuit of Fig. 5(a) may offer utility for neuromorphic computing. For the case of the PND, the number of nanowires in the array is on the order of the number of photons required for threshold. This is also the order of the number of connections each processing unit makes to other units. Biological systems reveal that scaling to systems with thousands of connections per neuron is desirable [16]. To achieve this number of parallel receiver elements, several geometrical configurations can be utilized to arrange approximately

1000 micron-scale SNSPD elements, and the exploration of this design space is the subject of future work.

The SND device straightforwardly lends itself to hundreds or thousands of connections. In this case, we can expect the thresholding number of photons to be approximately 1000, and, therefore, we want a nanowire with the length of 1000 hot spots. Given the hot-spot length of 100 nm, the entire length of the nanowire is on the order of 100  $\mu$ m, as simulated in Fig. 6. Such a length becomes quite compact when coiled in a spiral [see Fig. 11(b)], and as we discuss in Sec. III A, this configuration is well suited to receive inputs from hundreds to thousands of waveguides. We discuss the energy requirements of the SND and PND circuits in Sec. II F.

## D. The nTron current amplifier

Introducing an amplifier into the circuits described in Secs. II B and II C allows decoupling of the firing threshold and LED gain. In a superconducting circuit, amplification can be achieved using the nTron, a three-terminal supercurrent amplifier [53]. When the current in the gate terminal exceeds the critical current, the path from the source to drain is driven normal, diverting the bias current to the parallel load. This recently developed device has been used to drive loads of tens of kilohms, making it suitable for this application.

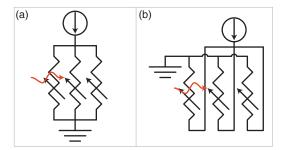

In Fig. 7(a), we show a variation of the circuit of Fig. 2(a), but instead of driving the same current  $I_1$  through the LED after firing, this circuit utilizes a nTron current amplifier to provide gain to the light emitter. The nTron allows us to decouple the current used to bias the receiver from the number of photons produced in the firing event. Note that in this configuration,  $I_2$  can be less than  $I_1$ , making it possible to cover a broad range of input-output responses. The circuit of Fig. 7(a) also expands the state space in which information can be encoded.

### E. Other neuromorphic circuits

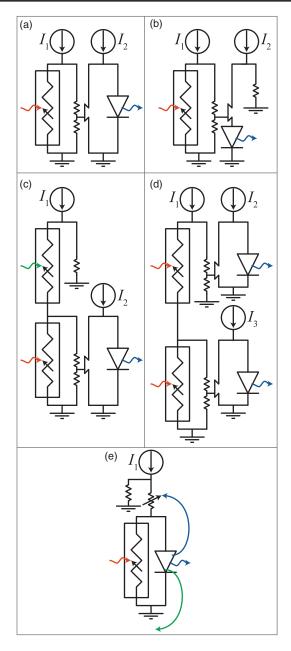

We introduce the basic neuromorphic circuits in Secs. II B and II C. We now introduce several variants on those cells which enable diverse functionality desirable for neuromorphic computing.

Figure 7(b) shows an alternate configuration in which the LED is driven by current  $I_2$  until a firing event occurs and cuts off the current supply. This circuit is shown with the LED below the nTron, but it can also be implemented without a nTron. This circuit is an example of an integrate-and-stop-firing neuron which can be useful in neuromorphic architectures to provide a means of stimulating various regions of the cortex until a certain level of activity is reached, at which point the firing neuron is quenched.

Another essential functionality of neuromorphic circuits is that of inhibitory connections [54,55]. Most neuronal connections provide feedforward excitation wherein an action potential produced by upstream neurons increases

FIG. 7. Various neuromorphic circuit configurations. (a) PND with nTron amplifier. (b) Integrate-and-stop firing. (c) Neuron with the possibility for both excitatory and inhibitory excitation. In this figure, green corresponds to photons inhibiting firing and red to photons exciting firing. These photons can have different colors. (d) Firing of the upper neuron inhibits firing of the lower neuron. (e) Circuit for achieving self- and upstream feedback.

the probability of action potentials being produced by downstream neurons. But biological systems also exhibit connections wherein the firing of upstream neurons suppresses the probability of firing events by downstream neurons. Figure 7(c) shows a configuration which achieves this. The lower portion of the circuit is identical to that of Fig. 7(a), but the current  $I_1$  feeding the receiver first passes through a preliminary nanowire array. Absorption of

photons in this region of the circuit reduces the current through the primary receiver, increasing the threshold photon number. Waveguides from different upstream neurons can be routed to these two different ports to establish inhibitory or excitatory connections. In Fig. 7(c), the inputs to the two receivers are drawn with different colors, emphasizing the possibility that integrated-photonic filters placed before the neuron can be employed to route different frequencies to the two receivers. With this approach, we can employ the use of color to perform inhibitory or excitatory functionality in much the same way that different neurotransmitters perform inhibitory or excitatory functions in biological systems [54]. We note that low-loss spectral filters performing this function are commonplace in many integrated-photonic applications.

From an architectural standpoint, it may also be useful to establish purely electrical inhibitory connections. In Fig. 7(d), we show a circuit in which two neurons, each with only a single excitatory port, are connected in series. In this configuration, firing events in the upper neuron inhibit firing events in the lower neuron. Such a configuration is useful for moderating the net firing activity of groups of neurons.

It is also advantageous to have a means by which a single neuron can moderate its own firing activity. Such behavior is straightforward to implement, as is shown in Fig. 7(e). A power tap is added to the output of the LED, and some fraction of the produced light is incident upon a receiver in series with the current supply to the receiver array. The superconducting wire in this location may be wider than the integrating receiver, and it, therefore, may be designed to quench the current only when a large number of photons drives the superconducting wire normal.

In addition to self-feedback, biological neurons send both downstream signals as well as upstream signals when an action potential fires. The upstream signals are believed to be critical for spike-timing-dependent plasticity and synchronization of circuit behavior via threshold modification. To briefly hint at how self-feedback may be implemented in the proposed platform, the green arrow leaving the LED in Fig. 7(e) indicates that a power tap can also be used for upstream feedback. The color of this arrow is meant to remind us that it may be advantageous to use different frequencies of light for downstream and upstream signaling. A LED can be fabricated to emit at two distinct wavelengths or across some region of bandwidth, and integrated spectral filters can be employed to route the two signals. Alternatively, two different LEDs coupled to two different waveguides can be utilized.

In this section, we present several superconducting optoelectronic neuromorphic circuits covering a wide range of functions. We refer to members of this class of circuits as single-photon optoelectronic neurons (SPONs). We now proceed to discuss additional aspects of their performance.

## F. Energy consumption

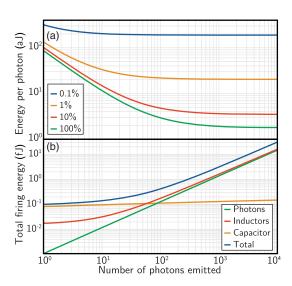

We introduce the basic SPON circuits of the proposed neuromorphic computing platform, and we are in a position to estimate the energy required for a firing event. A complete neuron firing event involves supplying current to the inductors associated with all superconducting wires (including the detectors), charging the capacitor associated with the LED *p-i-n* junction, and driving current through the LED to produce light. For the case of the PND circuit of Fig. 7(a), we analyze the energy consumption of each of these three contributions.

In this model, we assume one inductor  $L_{\text{SNSPD}}$  in the PND array for each photon, as well as a series inductance to achieve the desired temporal response (see Appendix A). We assume each element of the PND is 500 squares, while the entire receiver array is in series with 5000 squares of inductance. At low photon numbers, the energy consumption from inductance is dominated by the series inductance, but for higher numbers, it is dominated by the PND array and grows linearly. The energy required for photon production is calculated simply as  $E_g n_{\nu}/\eta$ , where  $E_g$  is the band gap of Si,  $n_{\nu}$  is the number of photons created, and  $\eta$  is the efficiency. Thus, within this model, the contribution to energy consumption due to photon creation is linear throughout. We use  $E_a$  in this model because it is an upper bound on the photon energy. Any photon transmitted through a Si waveguide will have energy below the band gap. We assume a superconducting material with a sheet inductance of 400 pH/□ (such as WSi), and a parallel-plate capacitive model for the LED as described in Appendix D.

In Fig. 8(a), we plot the total energy per photon as a function of the number of photons emitted for four values of LED efficiency. We find that with a unity-efficiency

FIG. 8. (a) Energy required to generate a single photon versus number of photons emitted for four different LED efficiencies. (b) Contributions to total energy consumption for a 10% efficient LED.

LED, the energy per photon can be as low as 2 aJ when larger photon numbers are created. This remarkably low number is still an order of magnitude greater than the 0.16 aJ stored in the  $h\nu$  of the light quantum itself (assuming  $\lambda = 1.22 \mu m$ ), with the extra energy going to supplying current to the inductors and charge to the capacitor. The figure reveals that producing LEDs with efficiency above 10% has only a modest benefit, as the contribution to energy consumption from inductance will become the limiting factor. However, for thresholding on larger photon numbers, as is desirable for neurons with more connections, the inductance per photon can likely be reduced. While a 100% efficient LED may not be realized, even a 1% efficient LED leads to 20 aJ/synapse event. This energy efficiency illustrates the promise of superconducting electronics and faint-light signals.

In Fig. 8(b), we show the contribution to the total energy from the various circuit elements for the case of a 10% efficient LED. This efficiency is chosen for this plot because it is the value at which the contributions from inductance and photon production are nearly equal for photon numbers near or above 100. For low photon numbers, the dominant contribution is in charging the LED capacitor. Because of the highly nonlinear LED current-voltage relationship, a small increase in the voltage across the LED leads to a large gain in current. The capacitive energy is nearly constant across the range of photon numbers considered here, and for larger photon numbers, it makes a negligible contribution.

In the case of the SND circuit of Fig. 5 with parameters as shown in Fig. 6(b) driven at 0.6  $I_c$  and receiving  $10^3$  photons, and assuming a hot-spot recovery time of 50 ns and a LED with 1% efficiency, the device achieves 100 aJ/synapse event. While not as efficient as the PND neuron, this device design still lends itself to massive scaling, as we discuss in Sec. IV B.

We believe a LED with 1% system efficiency is realistic in a nanophotonic environment at cryogenic temperature and with faint-light levels desired. Therefore, we use 20 aJ/photon as a representative number for what this platform can hope to achieve. We use the energy per photon as the energy per firing event per synapse (commonly referred to as the energy per synapse event), because the goal of the system is to produce neurons which threshold on a number of photons roughly equivalent to the number of connections made by the neuron. A neuron receiving 100 signals from upstream will threshold on 100 photons. It will produce 100 photons in a firing event and distribute them amongst 100 downstream synapses. Therefore, the energy per synapse event is calculated as the total energy of the firing event divided by the number of connections. In our case, for systems with 100 to 10 000 connections per unit, 20 aJ/synapse event is a realistic number.

The second law of thermodynamics informs us that to keep a system at 2 K, 150 W of cooling power is required

per watt of power dissipated at 2 K. Assuming a 15% efficient cooling system, this gives an estimate of 1 kW of cooling power per watt of device power. Multiplying our conservative estimate of 20 aJ/synapse event by this factor of 10<sup>3</sup>, the hardware achieves an energy consumption of 20 fJ/synapse event. Similarly, while the human brain uses 20 W to perform roughly 10<sup>14</sup> synapse events per second, a power budget of 20 W corresponding to 20 mW of device power will enable our system to achieve 10<sup>15</sup> synapse events per second. Success in developing LEDs with higher efficiency, reduction of the device inductance, and utilization of superconducting materials operating at higher temperatures will further increase the advantage. Additionally, while transistor technologies inevitably leak current, superconducting devices can be engineered to draw no power in the steady state and can be dc biased without loss using Josephson junctions [19].

# G. Electrically injected light source

Having introduced the proposed optoelectronic neuronal circuits, we now proceed to analyze the operation and performance requirements of the LED. As we discuss in the previous section, we target operation efficiencies of around 10%. This efficiency is relatively easy to attain in III-V semiconductors such as GaAs and InP. However, for the application at hand, massive scaling is a priority, and massive scaling requires photonic electronic process integration. A single source with 100% efficiency is less desirable than the ability to scale to millions (and eventually billions) of sources each with 1% efficiency. We also require low-loss waveguides with the potential for reconfigurability (see Sec. III).

One option is to implement these devices on a GaAs or InP substrate. These have been the materials of choice for photonic integrated circuits where light sources are of the utmost importance. Quantum-dot-well LED lasers can be electrically injected with high efficiency on this platform [38] and combined with high-index (III-V) waveguides to form the synaptic connections described in Sec. III A. Another option is to implement the light sources in the III-V material and then couple to low-temperature deposited materials with low-loss waveguides [46,56] such as a-Si or SiN. A III-V platform has the advantage of high-efficiency light sources, but massive scaling on III-V substrates has historically been more difficult and expensive than on Si substrates. This drawback, while not fundamental, may prove significant in halting the development of this technology, especially since high emitter efficiencies are not a strict requirement for neuromorphic computing.

Another option is hybrid III-V silicon integration. Hybrid III-V silicon has followed one of three approaches 57]]: direct mounting, wafer bonding, or III-V material grown on Si. While direct mounting or wafer bonding are currently the preferred methods for optical interconnect applications, these applications typically require a single

source that can be diverted to multiple components. For the proposed neuromorphic computing platform, we desire a separate electrically injected source for each neuron. Direct mounting, therefore, is not an option, but wafer bonding may be able to achieve the yield and reproducibility required for this application. Direct heteroepitaxial growth offers the most promise for hybrid integration with this system. In this case, the desired light source is templated III-V quantum dots grown in the intrinsic region of a lateral Si *p-i-n* junction. While great progress in this field has been made [58-64], additional effort is needed to achieve the waveguide-integrated sources required for this system. Promisingly, electrically injected single-photon emission has been demonstrated in these materials [58-61]. While single-photon emission is not a requirement for the present application, a desirable property of the emitters is that they have low-photon-number variance (defined as the standard deviation of the number of photons output for a given input current pulse over an ensemble of measurements). The fact that single-photon emission has been demonstrated in various systems indicates the possibility to bring this photon number variance down to the range of a few photons.

A major disadvantage of this heteroepitaxy approach is the significant cost and difficulty associated with growing these materials. As this approach matures, this material platform may become more desirable. Another similar approach using Ge [65] or Ge quantum dots [66] may also prove useful.

A commonly overlooked light source that may prove particularly promising for this application is emissive centers in Si [67]. These have proved unattractive for optical interconnects due to very low efficiencies at room temperature. Much work in this area was motivated by the prospect of room-temperature light sources [68] for CMOS and telecommunications [69] and, in particular, roomtemperature lasers. This includes various point defects in Si including Er [70-73] and other emissive centers giving rise to electric-dipole-mediated transitions [67,74–82], as well as band-edge or Si nanocrystal-based emission processes [83–85]. While the efficiencies of many of these emitters fall off exponentially with increasing temperature, the SNSPDs required for this application operate at cryogenic temperatures where many point defects have suitable efficiencies. A large number of emissive centers are under consideration for this application [67].

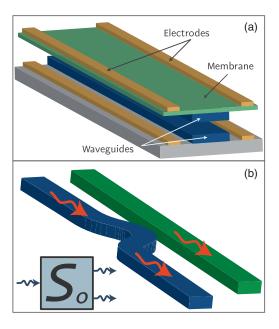

The main challenge is the successful integration of large numbers of emitters with the ultimate goal being billions integrated in a system. Many emissive centers can be easily fabricated in a CMOS-compatible process via ion implantation and annealing [67,75,80–82,86,87]. A schematic of the desired device is depicted in Fig. 9. A *p-i-n* junction is created in a ridge waveguide. Emitters are located only in the ridge (intrinsic) region via lithographic patterning, and light is obtained from forward biasing the junction. While

FIG. 9. Schematic of a monolithically integrated electrically injected emissive-center LED in Si for the proposed neuromorphic computing application.

this is a relatively standard configuration of a LED, for the application at hand it is important to keep the emitters localized only in the intrinsic region of the LED, as their presence elsewhere in the waveguides leads to intolerable loss. Thus, the ability to lithographically control the location of emitters is crucial.

With coimplantation of multiple impurities, it is possible to add additional (color) degrees of freedom to the platform. Similarly, on a III-V platform, we can take advantage of inhomogeneous broadening of the quantum-dot spectrum and tuning of dot size via templating or growth conditions.

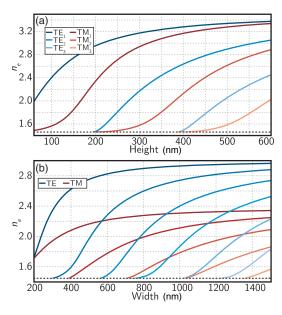

We note that the neuromorphic computing platform proposed here is not tied to any one of these light sources, and indeed there are other possible light sources that we have not discussed. For the calculations throughout the present work, we assume LEDs with 1% efficiency at  $1.22~\mu{\rm m}$  in a waveguiding medium with index of 3.52 with a cladding of 1.46 above and below.

### H. Summary

We have now presented several superconducting optoelectronic circuits capturing a broad range of neuromorphic behaviors. We have presented basic thresholding SPON circuits of Figs. 2 and 5, variants on these circuits as shown in Fig. 7 which enable gain, integrate-and-stop, and inhibitory connections, and circuits with self- and upstream feedback, as shown in Fig. 7(e). We now discuss the means by which we propose to connect these processing units.

### III. CONNECTIVITY

Of central importance to the implementation of the proposed neuromorphic platform is the network of waveguides that connect the processing units. Optical waveguides offer the possibility for improved performance over electrical connections by allowing individual neurons to integrate signals from many sources without the need for time multiplexing. Because of the additional energy cost associated with the capacitance of additional wires [88], electrical neurons must utilize shared wires. Voltage pulses from different neurons on the same bus will interact. To prevent this, pulses must be delayed in time.

In the following section, we discuss how a network of optical waveguides can be implemented to form the connections between the SPON circuits presented in Sec. II. Each neuron has a waveguide exiting the LED and leading to many branching waveguides, which we liken to the axon and its arbor, and another set of integrating waveguides combining signals received from upstream neurons, which we liken to the dendritic arbor, as shown schematically in Fig. 1. The connections between these input and output waveguides act as synapses in this network. We outline a mechanism for varying the strength of the connections between various input and output waveguides, which is similar to varying synaptic weights in biological systems. We emphasize that other methods of connecting neurons in three dimensions using the same optoelectronic neurons are also possible. One can envision using gratings, flat lenses [89], metasurfaces [90,91], or optical phased arrays [92,93] to direct signals between neurons. Additionally, electrical means of changing synaptic weights at the receivers may prove useful.

### A. The dendritic arbor

The dendritic arbor of a neuron collects signals from upstream neurons. For optoelectronic neurons, the equivalent of this is a waveguide network that combines optical signals from many other neurons to the neuron for detection. At each neuron, the device must be designed to combine the modes from a large number of waveguides on a PND or SND with low loss. There are likely many ways to achieve this functionality, and here we explore two.

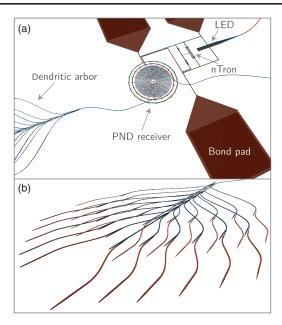

A schematic of the first approach is presented in Fig. 10(a) showing the spiral waveguide receiver of the spiderweb SPON, the nTron, and the LED emitter. The major challenge of this device design is the merging of many single-mode waveguides into one multimode waveguide which enters the spiral. The proposed technique for accomplishing this is shown in Fig. 10(b). Two singlemode waveguides cannot be combined into one singlemode waveguide without significant loss [94]. However, two single-mode waveguides can be combined into one dual-mode waveguide nearly losslessly. In Fig. 10(b), several single-mode waveguides combine their power on a given main spine. That spine can receive at its input one single mode. As it continues to receive more modes, its width must grow. The lower-order modes of this adiabatically tapering multimode waveguide can pass each new single-mode input nearly losslessly as long as the width of the spine has grown to support an additional mode by the location of the next input waveguide. More detail regarding the optical design of this structure is given in Appendix E. Modal simulations reveal that a waveguide width of 2  $\mu$ m in 200-nm-thick Si is sufficient to support several tens of modes at 1220-nm wavelength, each with tolerably small bending loss with a 10-µm radius of curvature. Therefore, this dendritic arbor and receiver design is suitable for the

FIG. 10. The spiderweb neuron. (a) Overview of the device. (b) Dendritic arbor design which combines light from multiple neurons.

compact combining signals from approximately 40 upstream neurons.

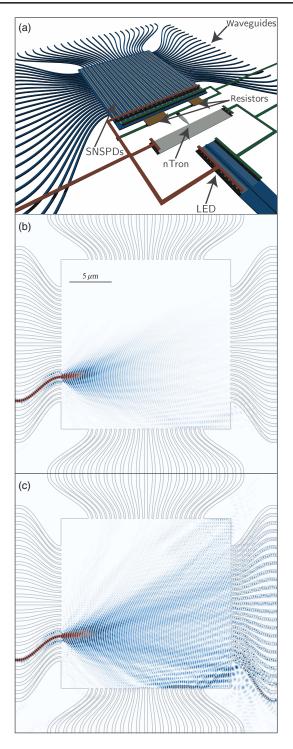

The second proposed design is better suited to scaling to larger numbers of inputs. It is shown in Fig. 11. In this design referred to as the stingray SPON, the input waveguides are directly combined on a landing pad housing the PND or SND array. The implementation with a PND is shown in Fig. 11(a). As is shown in Appendix E, the minimum spacing required to avoid modal coupling is 600 nm at the input of the cell. From these input ports, the waveguides enter an array of sine bends where their spacing is reduced to enter the smaller landing pad containing the nanowires. In this sine region, intermodal coupling is tolerated (and perhaps even desirable to spread the photons across the nanowires), as all waveguides ultimately terminate on the detector array. Figures 11(b) and 11(c) show 2D finite-difference time-domain (FDTD) simulations of the structure. Figure 11(b) shows the propagation of light into the receiver body in the presence of absorbing nanowires, while Fig. 11(c) shows propagation without the absorbing nanowires. Here, 100 waveguides terminate on a receiver body with less than 0.2-dB insertion loss from any port, with the outermost ports giving the most loss, and the innermost ports achieving near-zero insertion loss. In this context, insertion loss refers to light entering and leaving the simulation without being absorbed in the nanowire array. Calculated quantitatively with pulsed excitation, we find the majority of loss is due to light scattering and not entering the detector array rather than being transmitted through the receiver due to inadequate absorption. The entire receiver of Fig. 11(b) occupies  $30 \times 30 \ \mu \text{m}^2$ .

FIG. 11. (a) Schematic overview of the stingray neuron. (b) FDTD simulation of the dendritic arbor for the stingray neuron with SNSPDs present to absorb the light and (c) without SNSPDs present.

A design with 204 input waveguides and less than 1-dB insertion loss with a footprint of  $60 \times 60 \ \mu m^2$  is also found. For larger numbers of inputs, the simulations become cumbersome. Yet, scaling to larger systems is clearly possible.

For threshold-based computation, processing units with large numbers of connections are advantageous [16,95]. Biological systems achieve massive interconnectivity with 3D branching networks and dedicated wires for each connection. To achieve this level of massive interconnectivity, we propose the use of multilayer photonics. Recent work has demonstrated the utility of low-temperaturedeposited dielectrics [46,96] and superconductors [46] for scalable integrated photonics. For future massive scaling, we propose the use of waveguide routing networks and dendritic arbors spanning several—and possibly up to tens—of photonic and superconducting layers. A hybrid of the aforementioned spiderweb and stingray neuron designs can be implemented in which higher vertical-mode orders are utilized as well as higher lateral-mode orders, and massively multimode waveguides deliver their photon pulses to SNSPD receivers. These receivers can be implemented between waveguiding layers. At present, the technical challenge of building networks with processing units supporting tens to hundreds of connections is a serious one, so we mention the fully 3D multilayer photonic approach [97] to emphasize that this neuromorphic platform holds promise for scaling far into the technological future, but such sophisticated processing is not required to implement even very advanced systems with 2D interconnectivity supporting hundreds of high-bandwidth connections per unit.

### B. The axon and its arborization

The output waveguide (axon) from a unit's LED must split into as many branches as there are connections to be made. While such a power splitter may seem to be the timereversed case of the dendritic arbor, the initial conditions make this device significantly easier to implement. In the case of the dendritic arbor, one cannot assume the optical field will populate the arbor modes in a particular manner. Thus, while a power splitter can readily couple from a single-mode waveguide into many other single-mode waveguides, multiple single-mode waveguides cannot simply merge their power into a single-mode waveguide unless a particular distribution of power is present in the input waveguides. Such power splitters [98] can be made with a small footprint and low loss. It is straightforward to generalize such power splitters into the third dimension with multilayer photonics, and such an implementation will enable thousands of synapses with a volume of  $10 \, \mu \text{m}^3/\text{synapse}$ .

## C. Learning, reconfiguration, and plasticity

An important aspect of any neuromorphic computing system is the ability to establish the strength of interaction between the connected units. These connection strengths, often referred to as the weight matrix, are important for memory and learning. This weight matrix determines how much of the light from the firing of a particular neuron is

coupled into any other neuron, analogous to the synaptic strength between two neurons in a biological system.

As a first implementation, fixed connection weights are quite useful for many computing applications [9]. This can be readily accomplished by branching the output waveguide from one neuron and routing those waveguide branches to various downstream target-neuron input waveguides.

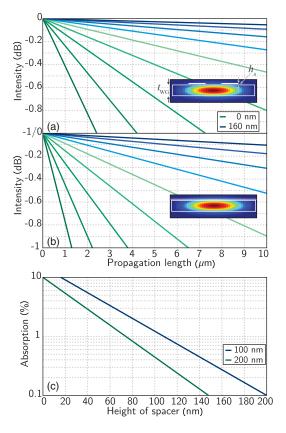

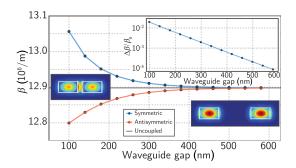

However, while fixed interaction weights are useful as a preliminary tool, one wants to develop a system in which the interaction strengths are variable. This is challenging at cryogenic temperatures, where modulators that rely on either the thermo-optic effect or free-carrier injection are ineffective, while electro-optic switches require too much space for this application. We propose the employment of electromechanically actuated waveguide couplers schematically depicted in Figs. 12(a) and 12(b). The amount of light coupled from one waveguide to the other is determined by the distance between them. These waveguides can be coupled either vertically [Fig. 12(a)] or laterally [Fig. 12(b)]. This distance can be controlled electromechanically, and anywhere from 0% to 100% of the light can be coupled from one waveguide to the other. The minimum coupling will be set in hardware, as the gap at 0 V is the maximum. Any applied voltage (positive or negative) produces an attractive force between the two waveguides. We then want activity within the circuits to build up voltage between the waveguides and increase the strength of the synapse. Such couplers have recently been demonstrated [99] in a highly scaled configuration. In Ref. [99], 4096 such switches were operated with >60-dB

FIG. 12. Photonic synapses with electromechanically tunable coupling. (a) Interplane waveguide coupler. (b) Lateral waveguide coupler. The inset shows an abstract representation of the synaptic circuit element used in subsequent network diagrams.

extinction ratio and actuation voltage of 40 V. Because of the relaxed visibility requirements for this application, we expect much lower voltages will suffice.

To assess the utility of such synapses for neuromorphic computing, one must further specify the target application. To this end, we separate potential applications into two classes, which we refer to as supervised and unsupervised systems. For supervised systems, an input stimulus is injected into the system, the output is recorded, and the weight matrix is updated through a training algorithm to improve the output relative to a target. For such an application, one anticipates using control electronics to interface with the neuromorphic system, and arbitrary voltages can be applied to the various synaptic elements.

For more highly scaled implementations emulating the behavior of biological organisms, we turn our attention to unsupervised systems. Here it is important that each synapse be as small as possible to enable massive scaling, but it is also important that voltages be modest, as we want the activity in the circuits to be capable of reconfiguring the synapses. In particular, we want firing events from upstream neurons followed closely by firing events by downstream neurons to place charge on this MEMS capacitor (waveguide coupler) and thereby decrease the gap between the two waveguides and increase the optical coupling and, therefore, the synaptic strength. This coordinated charging of the membrane will accomplish spike-timing-dependent plasticity, an important learning and memory reinforcement mechanism in biological neural systems. In this mode of operation, we envision eliminating external control circuits and achieving the capacitor charging using integrated superconducting circuits to distribute current based on photon-absorption events. The storage of charge on a capacitor required for this device operation is very similar to dynamic randomaccess memory (DRAM), which is a mature technology. While implementing what is essentially spike-timingdependent DRAM with suspended waveguide membranes presents a technical challenge, it offers a promising means to implement truly neuromorphic learning within this optoelectronic platform.

While the size of mechanical waveguide couplers and the voltages required for their operation are commensurate with the requirements for scaling this technology, an implementation of variable synaptic weights which does not rely on mechanically mobile components will be advantageous. It may be possible to implement synapses in the electronic domain by making use of superconducting circuit elements or magnetic elements such as magnetic tunnel junctions or magnetic Josephson junctions [23]. Such an approach to memory will be investigated in future work. Additionally, we note that a variable weight can be achieved with a tunable Mach-Zehnder interferometer. However, the size of such devices makes them poorly suited to highly scaled systems.

### IV. NETWORKS AND SCALING

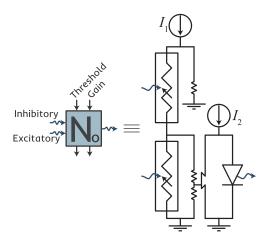

We have now discussed neural circuits based on optical signaling. We have discussed various means to connect these optical and electrical signals in a time-varying manner with event-based plasticity. In Fig. 13, we again show the inhibitory SPON of Sec. II C and introduce an abstract symbol to represent the circuit labeled  $N_a$ , which is used in the following sections as an element in networks. We refer to networks comprising interconnected SPONs as superconducting optoelectronic networks (SOENs). In this and the following schematics, we represent electrical inputs and outputs as black arrows running vertically and optical inputs and outputs as colored wavy arrows running horizontally. In Fig. 13, we emphasize that the optical processing unit can receive and transmit electrical and optical signals each in two ports. The electrical signals affect SPON threshold and gain, while the optical ports are either excitatory or inhibitory. This full functionality need not be employed, and as few as one optical input and output and one electrical input can be utilized.

We now illustrate how the circuits presented in Sec. II may be put to use in systems by considering the canonical example of the multilayer perceptron (MLP) in Sec. IVA. This leads us into a more general discussion of SOEN scaling in Sec. IV B.

# A. Multilayer perceptron

Perhaps the most studied implementation of neural networks is the MLP [49] and its contemporary counterpart, the convolutional neural network (CNN) [100]. Our consideration of the MLP provides insight into other applications of this platform in terms of important quantities such as speed, size, and dynamic range.

Generally speaking, the MLP consists of a number of inputs incident on a weight matrix (array of synapses) which feeds into a layer of neurons. The output of this layer of neurons projects to at least one more layer of weights and

FIG. 13. Abstract symbol definition for general neuron with inhibition and gain.

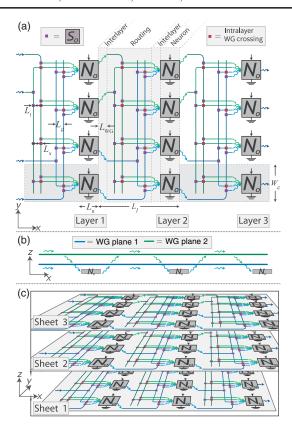

FIG. 14. (a) Schematic of the MLP implemented with the SOEN platform. (b) Cross section in the *x-z* plane. (c) Three-dimensional schematic of stacked die. (a) illustrates layers of neurons in the network, (b) illustrates planes of routing waveguides, and (c) illustrates sheets of stacked die.

neurons, and often several, before being output from the system. In Fig. 14(a), we show a schematic diagram of how such a MLP is likely to be implemented. Such a MLP can be achieved with a single plane of routing waveguides or many such planes. Here, we use "plane" to refer to vertically stacked dielectric layers to avoid confusion with the processing layers of the MLP progressing horizontally in Fig. 14(a). The processing layers of the MLP are labeled in Fig. 14(a), and the cross-sectional view of planes of routing waveguides is shown in Fig. 14(b). Stacked sheets of die are illustrated in Fig. 14(c).

Several factors determine the functionality of a MLP. These include the dynamic range of the inputs, the speed with which the inputs can be received, the bit depth of the synaptic weights, and the speed with which the weights can be reconfigured. From Fig. 6(c), we see that for 0.7  $I_c$ , the response turns on at around 500 photons, and it roughly levels out by 3000 photons. For this case, the dynamic range of the inputs is, therefore,  $\log_2(2500) \approx 11$  bits. The speed with which inputs can be received is limited by the device reset time of 50 ns, so a 20-MHz input rate is achievable. The bit depth of the weights depends on the number of discrete values of coupling achievable between the two waveguides involved in a synapse, and further investigation is required to

FIG. 15. (a) Length and width of layer versus number of neurons in a layer assuming each neuron in a given layer is connected to each neuron in the next layer. (b) Number of neurons per centimeter squared versus the number of connections per neuron.

report a valid estimate for this number. The speed with which the weights can be changed is at least 1 MHz [99].

The number of inputs, the number of connections per neuron, and the number of MLP layers all affect the size and complexity of MLP that can be fabricated on a given die. In Figs. 15(a) and 15(b), we consider a model of these factors to estimate what may be achieved with reasonable size. Figure 15(a) assesses the length  $L_1$  and width  $W_1$  of a single MLP layer, as given by Eq. (F1) as a function of the number of neurons in a MLP layer  $N_n$  for two different values of the number of vertically stacked waveguide planes  $N_{\rm WG}$ . The model assumes a feedforward configuration wherein every neuron in a given MLP layer is connected to every neuron in the next MLP layer with a variable-weight connection. The total width of a MLP layer is also plotted. See Appendix F for more information. If we assume that a  $10 \times 10$  cm<sup>2</sup> die is the largest we want to fabricate, we find the width limits the number of connections per neurons to 700, and we are, thus, considering MLP layers with 700 inputs and 700 neurons per layer. For the case with  $N_{\rm WG} = 10$ , the length of a MLP layer with 700 connections per neuron is 1 mm. We can, therefore, fit 100 such MLP layers on the  $10 \times 10$  cm<sup>2</sup> die. The total number of neurons is 70 000. A MLP or CNN with 700 inputs, 700 connections per neuron, and 100 layers receiving inputs at 20 MHz with weight reconfiguration speed of 1 MHz is a very powerful tool. While it is not necessarily optimal to work with a neural network of 100 layers, as shallower networks are advantageous for several reasons [95], we present this model to quantify SOEN

spatial scaling keeping in mind that network depth can be traded for a larger number of inputs or larger connectivity. As a point of comparison, the recent demonstration of a computer defeating the world champion Go player input the state of the board as a  $19 \times 19$  matrix (361 inputs) to the 13-layer-deep neural network [10]. The bit depth of the synapses proposed here is unlikely to reach the 32 bits utilized in software implementations running on modern graphics processing units, but there are likely many applications in which such a constraint is minor compared to the system advantages of speed, complexity, and connectivity.

# **B.** Scaling

To further pursue this discussion of the scaling of the MLP (or other similar neuromorphic computing systems), we consider the number of neurons in an area of 1 cm<sup>2</sup> versus the number of connections per neuron,  $N_{\text{conn}}$ . Figure 15(b) shows the results of the model of Eq. (F1) for  $N_{\rm WG} = 1$ , 10, and 100. If  $N_{\rm conn} = 10$  is sufficient for a given application, we can achieve a neuron density of 400 000 neurons per centimeter squared. Because of the size of the interlayer couplers, this is achieved more compactly with  $N_{\text{WG}} = 1$  than with  $N_{\text{WG}} = 10$ . For  $N_{\rm conn}$  in the range of 100 to 1000, it becomes advantageous to utilize  $N_{\rm WG} = 10$ . For  $N_{\rm conn} = 100$ , over 10 000 neurons will fit within a centimeter squared, and for  $N_{\rm conn} = 1000$ , 300 neurons fit within a centimeter squared. It does not become advantageous to use  $N_{\rm WG} = 100$  until  $N_{\rm conn}=2000$ , and even then the gain is modest. To achieve 10 000 connections per neuron (comparable to a mammalian brain), only a few devices fit within a centimeter squared (given the present model), and we are left in awe of the massive interconnectivity and scaling achieved by the bottom-up nanofabrication of biological organisms.

While the scaling to 10 000 connections per neuron is formidable, the range of  $N_{\text{conn}} = 100-1000$  is promising and technologically consequential. As is the case for scaling CMOS neuromorphic platforms, utilization of die tiling [9] plays a crucial role in this technology. For this purpose, the SOEN platform is in an excellent position. Die can be tiled in 2D with several types of connectivity to adjacent die including electrical, single-flux-quantum, and photonic communication over interdie bridge waveguides. Additionally, tiling in the third dimension is possible with the usual bump-bonding approach for electrical connectivity as well as with free-space optical signals sent from one chip using vertical grating couplers and received by a chip above or below using SNSPD arrays [101]. Information over such links can be encoded temporally, spatially, or in frequency with forgiving alignment tolerances. From Fig. 15(b), we find that 700 neurons with 700 connections per neuron can fit on a  $1 \times 1$  cm<sup>2</sup> die if ten waveguiding planes are utilized.

To analyze long-term scaling, we consider a system on the scale of the human brain. To this end, we envision tiling a  $215 \times 215$  array of these die in a sheet to build a system with  $32 \times 10^6$  neurons. Such a sheet will be approximately 1 mm thick. To achieve the scale of the brain, 2150 such sheets need to be stacked with intersheet coupling to construct a cube 2.15 m on a side and with a total volume of 10 m<sup>3</sup>. The system then comprises  $7 \times 10^{10}$  neurons or roughly the number contained in the human brain.

To achieve such a system, we envision sheets of die mounted in trays with in-plane fiber-optic connections leaving from the perimeter of the trays and out-of-plane free-space grating-to-SNSPD interconnects, thus, enabling the trays to slide laterally. Achieving intersheet connectivity without physical bonds enables access to die within the volume of the cube for diagnostics, repair, and local iteration and evolution. Massive interconnectivity between neurons on different die can be accomplished using such grating interconnects [89–93].

Of greater importance than the size of highly scaled systems is the power consumption. We again consider a system of SPONs with 700 connections each. Such a device consumes  $2 \times 10^{-17}$  J/synapse event, and with 700 connections, each firing event consists of 700 synapse events. Information processing in neuromorphic systems requires sparse event rates, so for the SOEN hardware wherein 20 MHz is achievable based on device limitations, 20 kHz represents a sparse rate. Note that this rate is a factor of  $(2 \times 10^4)$  –  $(2 \times 10^5)$  faster than biological event rates and a factor of 1000 faster than the CMOS demonstration which achieved 26 pJ/synapse event and was limited by time multiplexing [9]. For the system under consideration, we have  $7 \times 10^{10}$  processing units which we consider to be firing at this rate with this energy per firing event, giving a total device power consumption of 20 W. These numbers give  $5 \times 10^{16}$  synapse events per second per watt. The system must be kept around 2 K, so we also include an additional 1 kW of cooling power per watt of device power, as we discuss in Sec. II F. While this cooling power does not affect the power density (which ultimately limits scaling), and this 20 kW is minuscule compared to the tens of megawatts of a modern supercomputer, if we include this additional power in the calculation, we find that we achieve  $5 \times 10^{13}$  synapse events per second per watt.

To put this in perspective, the human brain also uses 20 W of device power, but by analogy to the inclusion of the cooling power in the above calculation, one must include the human's total power of 100 W which is necessary to sustain the brain's operational state. The brain has roughly  $10^{11}$  neurons with roughly  $7 \times 10^3$  synapses per neuron firing between 0.1 and 1 Hz [54,102–104]. For the purposes of this calculation, we generously assume the rate is 1 Hz. This equates to  $7 \times 10^{12}$  synapse events per second per watt. Even with the 1-kW/W cooling power of the cryostat, we find that the number of synapse events per

second per watt of the SOEN system exceeds that of the brain by an order of magnitude. The size of the SOEN system (10 m<sup>3</sup>, 2.15 m on a side) is, however, much larger than the biological brain.

Importantly, because signaling occurs predominantly in the optical domain, firing events can be directly imaged with a camera. For massively scaled systems, this direct optical imaging becomes a powerful metrological tool. Such a measurement technique can be used to monitor device and system performance across spatial and temporal scales in a manner analogous to functional magnetic resonance imaging of biological organisms.

To close this discussion of scaling, we address the cryogenic requirements of a 1-m<sup>3</sup> SOEN system. We seek a <sup>4</sup>He sorption refrigerator capable of cooling a 1 m<sup>3</sup> volume to 2 K with 20 W of cooling power. While this is a relatively large cryostat, it is certainly well within the realm of possibility. No new physical principles of operation need to be developed; it is simply a question of scaling up existing <sup>4</sup>He cryogenic systems. Additionally, if suitable SNSPD materials can be found which operate at 4 K with high yield, 20 W of cooling power is straightforward to achieve. We are of the opinion that with the advancement of single-flux-quantum processors, superconducting qubit devices, and SOENs, large-scale cryogenic technology will advance significantly in the coming years. Presently, many conversations in advanced computing debate whether the technology which proves victorious will operate within a cryostat or at room temperature. We speculate that a supercomputer of the future will leverage optoelectronic devices on various material platforms to employ quantum principles, neuromorphic principles, and digital logic principles across various temperature stages. The device designer is faced with the task of optimizing hardware performance at each temperature stage, and the architect is liberated to dream with von Neumann [5] far beyond the architecture that now bears his name.

# V. DISCUSSION AND OUTLOOK

We have explained the proposed devices and their functions, analyzed their performance, and considered their scaling. Here we consider possibilities for utilization of this platform for neuromorphic applications.

# A. Advantages of optoelectronic neural networks

The unparalleled performance of the brain emerges from the enormous number of connections between neurons and the numerous complex signaling mechanisms available to the neurons. Optical signaling has an advantage over electronics in terms of the ability to route noninteracting signals in three dimensions without wiring parasitics. These strengths have been recognized for many years, and early implementations utilized reconfigurable holographic gratings [105,106] for forming connections between

optoelectronic neurons [107]. We envision utilizing multilayer waveguides [97] in a deposited-photonics process [46] to implement photonic fanout [98] and routing from each neuron to its many downstream connections.

The two key components to enable photonic fanout and routing at an intradie level are multilayer waveguide power dividers and in-plane waveguide crossings. Both of these devices occupy a small area and operate with low loss and no *RC* penalty. As we mention in Sec. IV B, implementing these devices with roughly ten waveguiding layers appears optimal, comparable to the number of back-end-of-line metal layers used in CMOS for interconnect. With ten waveguiding layers, the desired routing between optoelectronic neurons still requires in-plane waveguide crossings [108]. The ability to implement multilayer power dividers and in-plane waveguide crossings with low loss and low cross talk allows dedicated communication lines for each interneuron connection.

On the receiving end, signals from an arbitrary number of SPONs can be received simultaneously, and time multiplexing is unnecessary. The system is conducive to encoding of information in both spike rate and timing. On an electronic platform, the length of an electronic signal line increases as the number of connections grows, resulting in a larger RC time constant. This increase in RC time constant with number of connections forces a speed or connectivity trade-off, leading most electronic neuromorphic implementations to share communication lines. Such a shared interconnect can transmit only a single voltage pulse within a time window, and this limits both the number of connections between neurons and the firing rate of each neuron.

Other approaches that leverage phenomena unique to optics for neuromorphic computing [109-114] have employed optical devices such as lasers and integrated microresonators. Laser cavities with strong light-matter interaction can be leveraged to realize complex nonlinear dynamics which can emulate the behavior of neurons [109,111,114]. The frequency selectivity of integrated ring resonators can be used to achieve synaptic weights [112]. Optical neural networks [113,115] and spiking neurons [111,116–119] based on these effects have been proposed and demonstrated. Optical reservoir computing has also recently been demonstrated [120-122] as another way in which inherently optical phenomena can be leveraged for advanced computing. The distinction of the proposed SOEN platform is that it operates in the few-photon regime with compact, energy-efficient components, enabling a large degree of scalability. Thus, at present, many electronic and photonic technologies appear promising for neuromorphic computing, and the most suitable hardware platform is likely to depend on the application.

### B. The visual cortex

While we describe in detail in Sec. IVA how a simple neural network (the MLP) can be built with SPONs, the

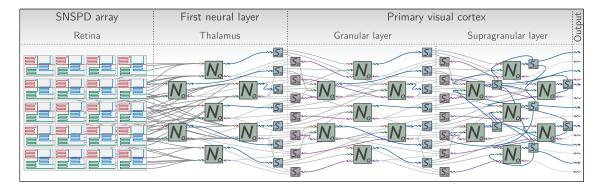

FIG. 16. Schematic of a SOEN model of the mammalian visual cortex.

potential of the SOEN platform for more complex systems should not be overlooked. The visual cortex is the most thoroughly studied region of the mammalian brain [123], yet there is still a great deal to be understood about information encoding from the retina through the thalamus and on to the visual cortex. A nonbiological experimental test bed is highly desirable to explore hypotheses [8,124]. Biologically realistic supercomputer simulations of the brain can simulate only a small fraction of the brain cells in a small mammal at significantly reduced speed [125,126]. The massive parallelism enabled by a scalable, biologically realistic hardware implementation of the many thousands of neurons involved in the visual system can provide more quick and efficient simulations [18,126,127], which may give further insight into the visual system, while also offering potential for image-processing applications.

We propose a hardware platform with the potential for a built-in retina, manifest as integrated SNSPDs, which can be used in pixel arrays [101] for monolithic image acquisition and analysis. In Fig. 16, we show a schematic of how such a SNSPD array can be integrated with a multilayer neural network to emulate the visual system. To illustrate the key points of such an experimental system, we break the visual system into three parts: the retina, the thalamus, and the primary visual cortex. In biological systems, the primary visual cortex is highly sophisticated, being organized into six layers each with their own sublayers [123]. For the purpose at hand, we treat the primary visual cortex as being composed of two layers referred to as the granular layer and the supragranular layer.