## Demonstration of a Wafer-level Hall-Mobility Measurement Technique

L.C. Yu<sup>1,2)</sup>, K.P. Cheung<sup>1\*)</sup>, V. Tilak<sup>3)</sup>, G. Dunne<sup>3)</sup>, K. Matocha<sup>3)</sup>, J.P. Campbell<sup>1)</sup>, J.S. Suehle<sup>1)</sup>, K. Sheng<sup>2)</sup>

<sup>1)</sup> National Institute of Standards and Technology, 100 Bureau Drive, Gaithersburg, MD 20899, USA

<sup>2)</sup> Electrical & Computer Engineering, Rutgers University, 94 Brett Rd, Piscataway NJ 08854, USA

<sup>3)</sup> GE Global Research, One Research Circle, Niskayuna, NY 12309 USA

In this work, we demonstrated a wafer-level Hall-mobility measurement technique that allows for a rapid survey of many devices. We further explore the possibility of extending this technique into a fast-pulsed Hall measurement to investigate the transient behavior of mobility.

Accurate characterization of channel inversion mobility is important for understanding carrier transport in MOSFETs. In the development of advanced/novel devices, such as high-k based MOSFETs, III-V channel material based devices, or even SiC power MOSFETs, improving channel mobility is often the first and foremost challenge. The ability to measure mobility accurately is the prerequisite for a clear understanding on the degradation mechanisms. Split-CV is the most frequently used mobility measurement method. It is not an easy measurement and its accuracy decreases when the device is ultra small¹ or when there is a high level of charge-trapping². While correction methods exist for split-CV in those situations¹.², the complexity of implementation is further increased. Hall-mobility measurement is an appealing alternative which is immune to the aforementioned shortcomings. However, other than being used as a calibration for the corrected split C-V measurement¹, it is not often used. Regular Hall mobility measurements are tedious. In addition to a bulky, expensive and dedicated setup, wafer dicing, wire bonding and device packaging inhibit frequent measurements. Any wide-ranging survey using a large number of samples requires a heroic measurement effort. In this work, we demonstrated a wafer-level Hall measurement method, which requires neither packaging nor a bulky/expensive system. It greatly reduces the efforts needed for Hall measurements and makes device characterization much more convenient. Using this technique, a fast pulse-gated Hall measurement is also possible, opening a new way to study the transient charge-trapping behavior in the gate dielectric and its interface.

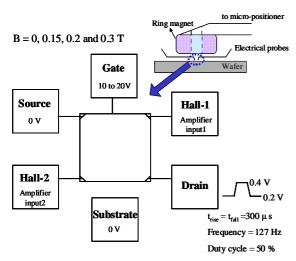

Fig. 1 Wafer-level Hall measurement set-up for the inversion sheet charge density (n<sub>s</sub>). 4H-SiC gated Van der Pauw structure is used, which has an active gate area of 150  $\mu$ m × 150  $\mu$ m.

In Hall measurements, a strong and uniform magnetic field is required. The key of our approach is the realization that such requirement can be satisfied by bringing a permanent magnet very close to the device. In our experiment, a donut-shaped permanent magnet with 3 mm inner diameter is placed above the device under test using a micro-positioner with high precision (25  $\mu m$  resolution), as shown in the inset of Fig. 1. The relationship between the magnetic field and the vertical separation distance is calibrated by a small (0.016 mm² active area) Hall Sensor. The maximum field achievable is about 3200 Gauss. We utilize this Hall set-up to examine 4H-SiC MOS-gated Van der Pauw/Hall bar structures with 150  $\mu m \times 150~\mu m$  gated area.

In order to get  $\mu_{Hall}$ , inversion sheet charge density  $(n_s)$  and sheet resistance  $(R_s)$  are measured separately. In the  $n_s$  measurement, the gate is kept at a certain potential, the source and substrate are grounded and the drain voltage is modulated from 0.2 V to 0.4 V by a 127 Hz square wave with  $t_{rise} = t_{fall} = 300~\mu s$ . The differential voltage between the two Hall terminals is measured using a differential amplifier (10  $M\Omega$  input impedance) and monitored with an oscilloscope along with the source current. The set-up is shown in

Fig. 1. The use of drain voltage modulation allows the signal-to-noise ratio to be improved rapidly by averaging. The short measurement time prevents complications due to device drift during the measurements. This is especially important when measuring SiC MOSFETs, which are known to have significant as-processed charge trapping and de-trapping<sup>3</sup>.

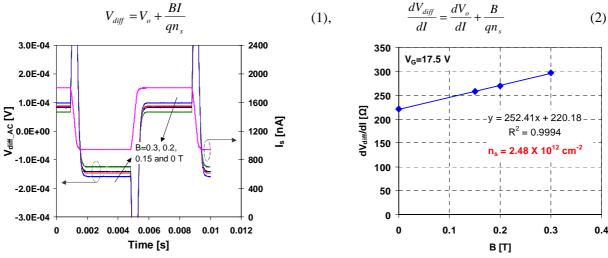

Fig. 2 shows the measured waveforms from the Hall terminals. The peaks at each transition are due to displacement current arising from some asymmetry in the device geometry. The asymmetry also produces an offset voltage in the measured differential voltage, as expressed in equation (1) where  $V_{diff}$  is the voltage difference between the Hall terminals,  $V_o$  is the offset voltage, B is the magnetic field, I is the drain or source current and q is the electron charge. While the voltage difference between the two flat regions ( $dV_{diff}$ ) is the sum of the actual Hall voltage change and the offset voltage change, only the change of Hall voltage gets larger as the magnetic field increases. Measuring the voltage difference at a few magnetic fields can separate the two contributions. Fig. 3 plots  $dV_{diff}/dI$  as a function of B field. According to equation (2) the inversion sheet charge density  $n_s$  can be directly extracted from the slope in Fig. 3.

Fig. 2 Source current and AC coupled differential voltage corresponding to the drain voltage modulation. Four magnetic fields are used

Fig. 3 Inversion sheet charge density ( $n_s$ ) extraction at  $V_G$ =17.5 V.

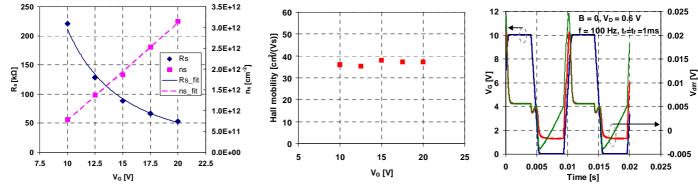

$R_s$  is measured using Van der Pauw procedures<sup>4</sup>. In Fig. 4,  $R_s$  and  $n_s$  are plotted as a function of gate voltage. The Hall mobility can be calculated from  $\mu_{Hall}=1/(qn_sR_s)$ . Fig. 5 shows the Hall mobility as a function of gate bias. It is not what one would expect for a high-quality MOSFET. It is almost independent of the gate voltage in the range investigated. Similar dependency has been reported on SiC devices measured by regular Hall systems<sup>5</sup>. The measured mobility is very small compared to the bulk value. This is also well known for SiC MOSFETs.

Fig. 4 Sheet resistance and inversion sheet charge density measured at different gate voltages.

Fig. 5 Hall mobility calculated from  $R_s$  and  $n_s$  as a function of gate voltage.

Fig. 6  $V_{\text{diff}}$  corresponding to a  $V_{\text{G}}$  pulse. The two  $V_{\text{diff}}$  traces are measured with one-minute separation.

One can also pulse the gate instead of the drain in the Hall mobility measurement. High-speed pulsing can potentially allow us to use Hall mobility as a probe for transient charge-trapping. Fig. 6 shows the preliminary results of  $V_{\rm diff}$  corresponding to a 100 Hz gate pulse from 0 to 10 V with rise and fall time of 1 ms. The two traces are measured with a one-minute separation. As discussed before, imperfection in device symmetry produces large displacement current induced peaks during switching and there is a long time constant associated with the  $V_{\rm diff}$  when the device is off due to high channel resistance. Obviously, several modifications must be made before fast measurement is possible. Smaller devices will help reduce the transients and are currently being fabricated. Keeping the gate voltages above  $V_{\rm th}$  can also help by avoiding very high channel resistance.

In summary, we have demonstrated a wafer-level Hall-mobility measurement method that does not require any wafer dicing, wire bonding, packaging nor the regular Hall measurement system. This method makes the device characterization and development much more convenient. With this method, transient behavior of the interaction between interface traps and channel carriers is studied by pulsing the gate. Modifications are suggested to further explorations.

<sup>&</sup>lt;sup>1</sup>A. Toriumi et al, International Electron Device Meeting, 2006, pp.1-4

<sup>&</sup>lt;sup>2</sup>W. Zhu et al, Electron Devices, IEEE Transactions on Vol.51 (2004), pp.98-105

<sup>&</sup>lt;sup>3</sup>M. Gurfinkel et al, IEEE Transactions on Vol.55 (2008), pp.2004-2012

<sup>&</sup>lt;sup>4</sup>D. K. Schroder, Semiconductor Material and Device Characterization, John Wiley & Sons, 2006

<sup>&</sup>lt;sup>5</sup>T. Hatakeyama et al, Materials Science Forum, Vols.483-485 (2005), 829-832