# Practical Aspects Impacting Time Synchronization Data Quality in Semiconductor Manufacturing

Naveen Kalappa, James Moyne, Jonathan Parrott, and Ya-Shian Li

2006 Conference on IEEE 1588

Official contribution of the National Institute of Standards and Technology; not subject to copyright in the United States.

Certain commercial equipment, instruments, or materials are identified in this paper to foster understanding. Such identification does not imply recommendation or endorsement by the National Institute of Standards and Technology, nor does it imply that the materials or equipment identified are necessarily the best available for the purpose.

#### **Outline**

- Why is time synchronization so important in semiconductor manufacturing?

- Components in the end-to-end synchronization problem

- Currents efforts in semiconductor manufacturing impacting time synchronization data quality

- NIST and the University of Michigan

- Key points and future efforts

## Time Synchronization and Manufacturing

#### Manufacturing Automation

- Process Control

- Coordination among tools

- Scheduling/Dispatching

**Fault Diagnosis for Power Industry**

**Robotics Coordination for Auto Industry**

#### Test and Measurement

– Fault DiagnosisNetwork Operations

- Security

- QoS measurement

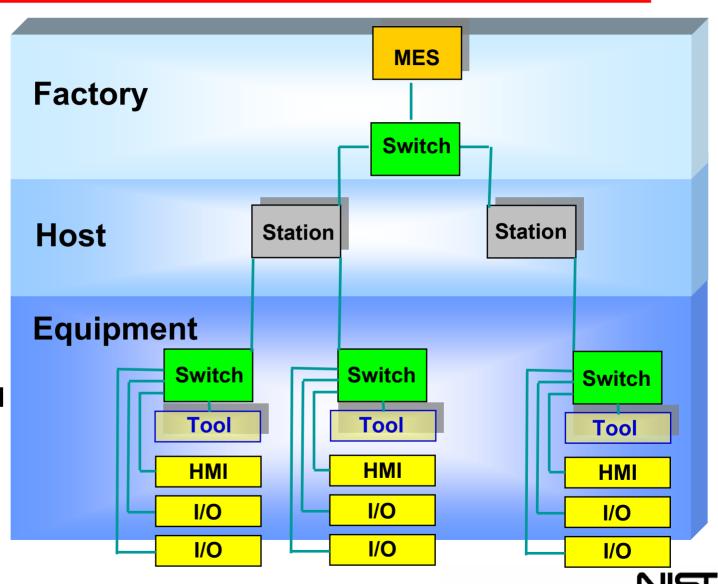

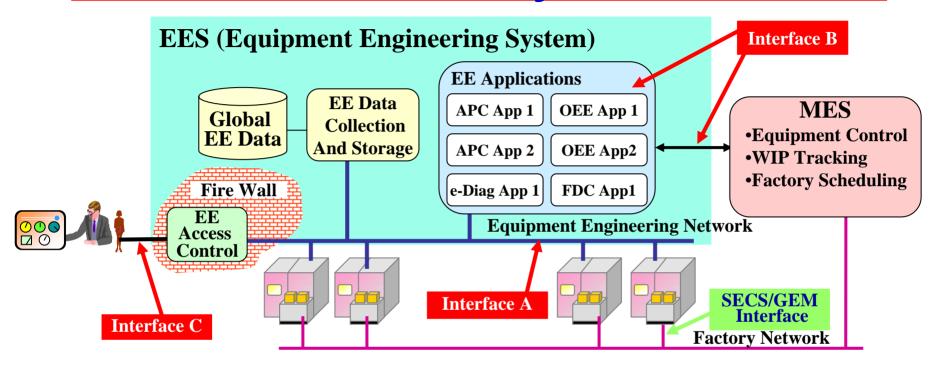

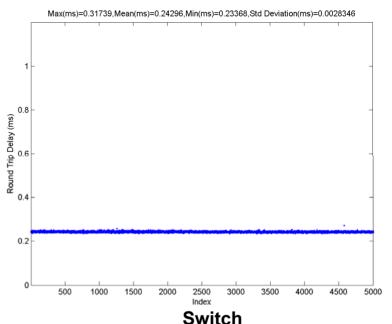

#### **Motivation: The Move to Networks**

## Ethernet Everywhere!

- InterfacesA, B and C

- EDA, PCS, e-diagnostics

- HSMS

- XML, VPN, OPC

- MES to I/O Level

## **Semiconductor Factory**

- •Interface "A" Components

- Process Control and Equipment Operational Data

- Host-Independent Data Collection

- Data Collection Plans → E134

- Equipment Self-Description → E125

- Authentication and Authorization → E132

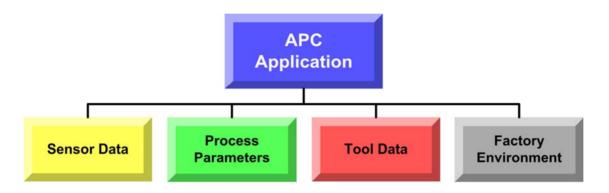

## **Motivation in Chip Manufacturing**

Precision Time Stamping to Merge Various Data Streams

#### **Advanced Process Control:**

- Fault Detection Classification (FDC)

- e-Diagnostics

- Process optimization

- Virtual metrology

#### Precision time-stamping and time synchronization:

- Merging data from heterogeneous sources

- Maintain data and event ordering

- Improve multivariate, advanced correlation and analysis

- Expose new cause-effect relationships

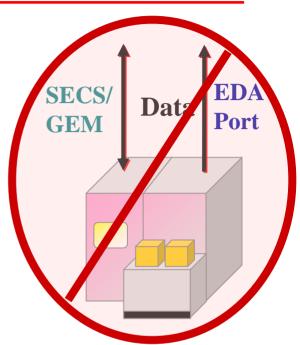

## **Common Time Sync. Pain Points in APC**

- Events and data are received out-of-order

- Inability to support high data collection rates with good data quality

- Cannot synchronize data across multiple systems (e.g., equipment & metrology systems)

- "False Positives" in fault detection systems bring equipment down unnecessarily

- Out-of-order data, poor time-stamping

- Time-stamping at point of sending instead of point of event occurrence

- "Out-of-control" situations for R2R controllers

- Poor data quality due to delay and <u>delay variability</u>

- Inability to migrate from the equipment level to the factorywide level with APC systems

- Etc...

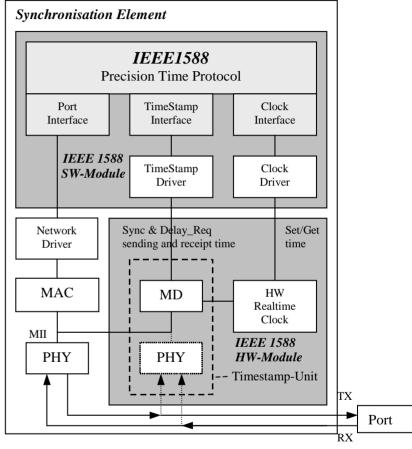

## **Solutions for Time Synchronization**

- NTP 4.0 or SNTP 4.0

- Software only

- 50 us to 50 ms accuracy, depending largely on software environment

- More mature

- ANSI/IEEE 1588 (IEC 61588)

- Software and hardware

- Approx 100ns accuracy

- Infancy in standard and solutions

necessary if no MII- interface available

MD – Message Detector for Sync and Delay\_Request packets

#### **Outline**

Why is time synchronization so important in semiconductor manufacturing?

- Components in the end-to-end synchronization problem

- Currents efforts in semiconductor manufacturing impacting time synchronization data quality

- NIST and the University of Michigan

- Key points and future efforts

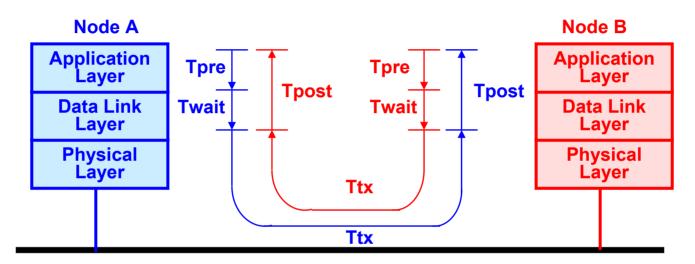

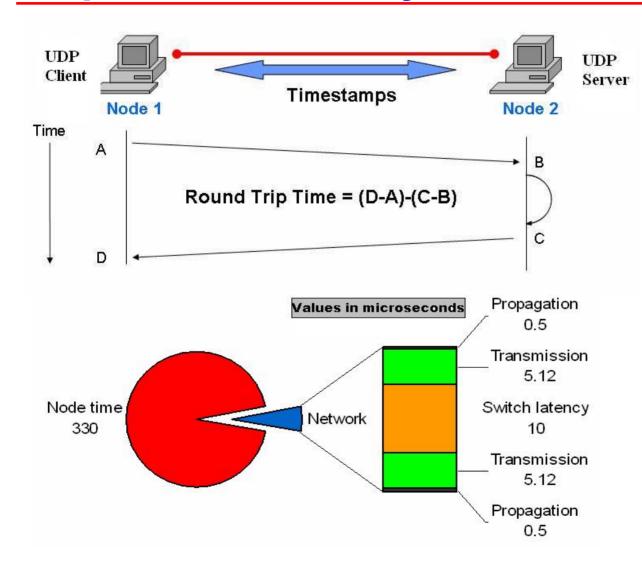

### **Components of Delay**

#### Where are the sources of delay and variability?

Network and nodes

Total end-to-end delay is the sum of

Pre-processing time: microprocessor

Waiting time: network protocol - MAC

Transmission time: data rate & length

Post-processing time: microprocessor

## **Experimental Analysis**

The Delay

is in the

Node Software

(Tpre, Twait

and Tpost)

## **Application level delays**

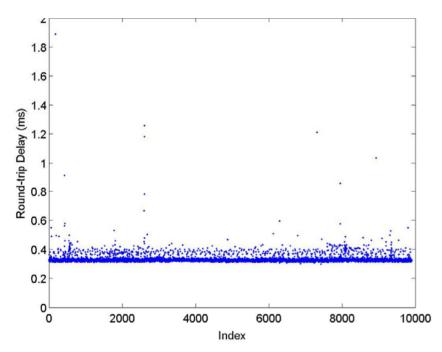

UDP round-trip delays (100Mbps switched network)

- Mean = 0.33ms, max = 1.89ms

- Stdev = 0.03ms

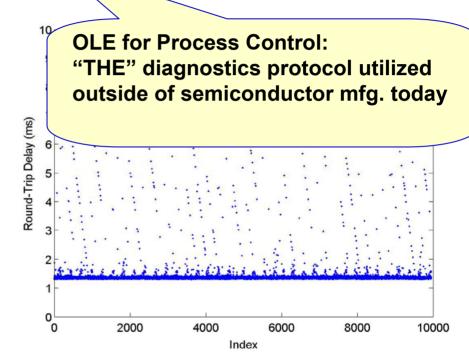

• OPC round-trip delays (100Mbps switched network)

- Mean = 1.5ms, max = 16.8ms

- Stdev = 0.81ms

The Delay and delay Variability is in the *Node Software*

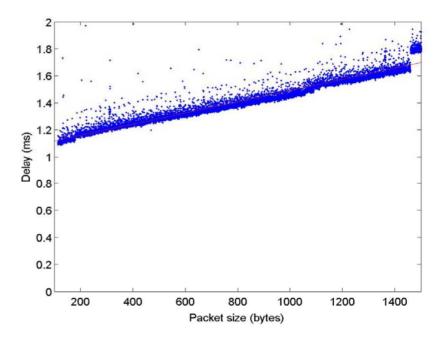

## Varying packet size

- UDP round-trip delays (100Mbps switched network)

- 1.8

1.6

1.4

(SE) 1.2

NOTE OF THE PROPERTY OF

- Slope = 0.411μs/bit

- Theory: 0.32 μs/bit

- Intercept: 0.285ms

VPN round-trip delays (100Mbps switched network)

- Slope = 0.848μs/bit

- Intercept: 1.07ms

- Using DES (data encrypt. std)

## **Network Delay Test Results**

|                                         | UDP   | VPN<br>(UDP) | OPC<br>(TCP) | DeviceNet |

|-----------------------------------------|-------|--------------|--------------|-----------|

| Delay Average (ms)                      | 0.33  | 1.21         | 1.48         | 0.3-1.2   |

| Delay Variation (3σ) (ms)               | 0.09  | 0.49         | 2.43         | 0.005-0.2 |

| Min. Network Delay<br>Contribution (ms) | 0.035 | 0.035        | 0.035        | 0.188     |

| % of Delay Due to Network               | 11%   | 3%           | 2%           | 63%       |

#### The Message:

- We need time synchronization and time-stamping to mitigate delay and delay variability disturbances of end-to-end network communication

- We need standards for time synchronization and when to timestamp information in the end-to-end communication path

- Using synchronization and time-stamping, we can decouple application node time from communication network time

#### **Outline**

- Why is time synchronization so important in semiconductor manufacturing?

- Components in the end-to-end synchronization problem

- Currents efforts in semiconductor manufacturing impacting time synchronization data quality

- NIST and the University of Michigan

- Key points and future efforts

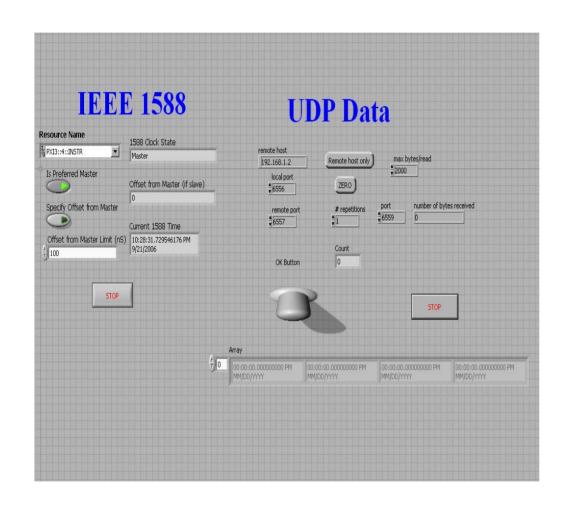

#### IEEE 1588 testbed in operation

- 1588 hardware I/O cards

- LabVIEW as the application software

- XML traffic generators

- Routines for encapsulation, e.g., VPN, OPC, UDP, as necessary

## Performance testing of IEEE 1588 for semiconductor manufacturing applications

- Data collection

- Event reporting

- Remote monitoring

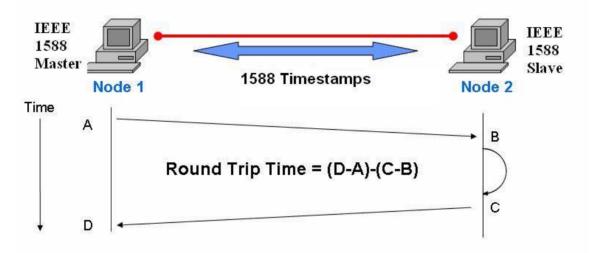

#### Tests with 1588

- Tests designed to see effect of 1588 time-stamping and synchronization

- Nodes synchronized through IEEE 1588 protocol

- Time-stamping through 1588 clock

- 1588 timestamps exchanged

- LabVIEW is used as the application layer for programming

- Time synchronization interval for PTP set at two seconds

- Interface through LabVIEW for accessing 1588 clock

- UDP data time-stamped with 1588 clock and exchanged

- UDP Round Trip time calculated from data exchange

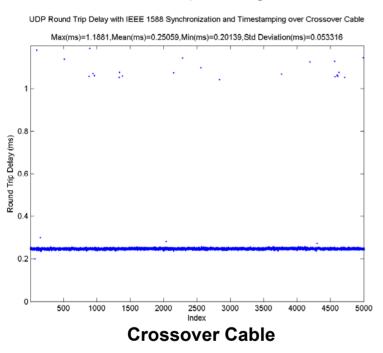

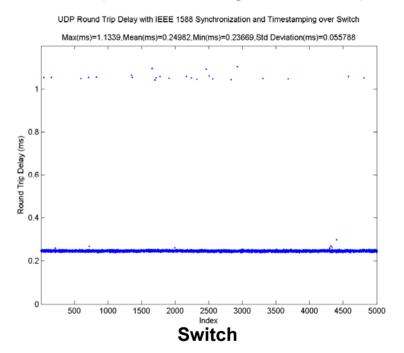

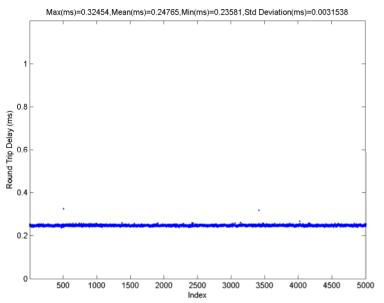

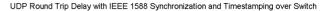

#### UDP Round Trip delays for 100 Mbps network (250ms delay between packets)

#### Values for 5000 packets with a delay of 250ms between packets

| `         | Max (ms) | Mean (ms) | Min (ms) | Std Dev (ms) |

|-----------|----------|-----------|----------|--------------|

| Crossover | 1.188    | 0.251     | 0.201    | 0.053        |

| Switch    | 1.134    | 0.250     | 0.237    | 0.056        |

#### UDP Round Trip delays for 100 Mbps network (1s delay between packets)

#### **Crossover Cable**

Values for 5000 packets with a delay of 1s between packets

| •         | Max (ms) | Mean (ms) | Min (ms) | Std Dev (ms) |

|-----------|----------|-----------|----------|--------------|

| Crossover | 0.325    | 0.248     | 0.236    | 0.003        |

| Switch    | 0.317    | 0.243     | 0.234    | 0.003        |

#### Summary of initial results

- With 1588 time-stamping, increasing the delay between packets led to lower values of jitter for the UDP round trip delay

- LabVIEW used on Windows (OS used) may introduce variability

- UDP data exchanged is time-stamped through the application (LabVIEW) GUI, no hardware timestamping of data

#### Future tests

Use Linux OS and 1588 time-stamping

#### Next Steps

Benchmark common protocol scenarios (XML, VPN, etc.)

- Interface "A" traffic volume analysis and performance benchmarking

- Simple equipment EDA traffic simulators

- APC scenario analysis

Traffic patterns similar to Interface A

#### Outcome

- Exploration of Time Synchronization for Semiconductor Manufacturing

- Identification of weak links in equipment, software systems, standards, etc.

- Input into SEMI standards effort

#### **Outline**

- Why is time synchronization so important in semiconductor manufacturing?

- Components in the end-to-end synchronization problem

- Currents efforts in semiconductor manufacturing impacting time synchronization data quality

- NIST and the University of Michigan

- Key points and future efforts

## **Key Points**

- Many efforts in implementing EDA and PCS implementation will fail if data quality is not addressed

- Lack of time synchronization and accurate time-stamping is a common source of poor data quality

- The weak link is often the tool software performance, so where you timestamp is very important

- NIST, The University of Michigan and SEMI are working together to address this issue, with the end result being standards and prototypes that will impact PCS, EDA and e-diagnostics

#### **Future Efforts**

- Identify and quantify the weak links in timing and time synchronization for APC

- Education

- When and how to apply time synchronization, and at what level

- Simulation of semiconductor factory environment

- Provide cost / benefit analysis

- What level of time synchronization is needed at various places throughout the fab;

e.g., is hardware time synchronization required?

- SEMI standards for time synchronization and time-stamping

#### Thank You!! ©

#### For further information

James Moyne: <u>moyne@umich.edu</u>

UM-ERC-RMS: <a href="http://erc.engin.umich.edu">http://erc.engin.umich.edu</a>

J. T. Parrott, J. R. Moyne, D. M. Tilbury, "Experimental Determination of Network Quality of Service in Ethernet: UDP, OPC, and VPN," *Proceedings of the American Control Conference*, Minneapolis, MN, June 2006.

#### Acknowledgments

- NIST

- NSF Engineering Research Center for Reconfigurable Manufacturing Systems (UM-ERC-RMS)

- ISMI and SEMI

- Jonathan Parrott and Dawn Tilbury

- Questions?