# NST

National Institute of Standards and Technology

Technology Administration

U.S. Department of Commerce

NISTIR 7368 January 2007 ELECTRONICS AND ELECTRICAL ENGINEERING LABORATORY

# SEMICONDUCTOR ELECTRONICS DIVISION

Programs, Activities, and Accomplishments

# THE ELECTRONICS AND ELECTRICAL ENGINEERING LABORATORY

One of NIST's seven Measurement and Standards Laboratories, EEEL conducts research, provides measurement services, and helps set standards in support of: the fundamental electronic technologies of semiconductors, magnetics, and superconductors; information and communications technologies, such as fiber optics, photonics, microwaves, electronic displays, and electronics manufacturing supply chain collaboration; forensics and security measurement instrumentation; fundamental and practical physical standards and measurement services for electrical quantities; maintaining the quality and integrity of electrical power systems; and the development of nanoscale and microelectromechanical devices. EEEL provides support to law enforcement, corrections, and criminal justice agencies, including homeland security.

EEEL consists of four programmatic divisions and two matrix-managed offices:

Semiconductor Electronics Division

Optoelectronics Division

Quantum Electrical Metrology Division

**Electromagnetics Division**

Office of Microelectronics Programs

Office of Law Enforcement Standards

This document describes the technical programs of the Semi-conductor Electronics Division. Similar documents describing the other Divisions and Offices are available. Contact NIST/ EEEL, 100 Bureau Drive, MS 8100, Gaithersburg, MD 20899-8100, Telephone: (301) 975-2220, On the Web: www.eeel.nist.gov

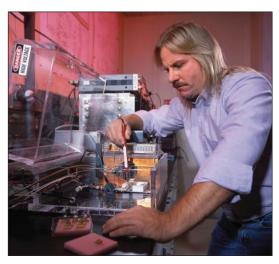

Cover caption: (clockwise from lower left) an IBM 200 mm EDRAM Wafer (photo by Tom Way, courtesy of International Business Machines Corporation, unauthorized use not permitted); optical micro-graph showing the complex film structure of a solution processed organic field effect transistor; visualization of the Electronic Information Group's efforts on developing standards for the manufacture of Semiconductor Electronics and Printed Circuit boards that are environmentally friendly; Division researcher Allen R. Hefner, Jr., performs high-speed, high-voltage silicon carbide device characterization using NIST-developed, specialized equipment; (background) nanowires grown on square-pattern gold thin film catalyst.

# ELECTRONICS AND ELECTRICAL ENGINEERING LABORATORY

# SEMICONDUCTOR ELECTRONICS DIVISION

PROGRAMS, ACTIVITIES, AND ACCOMPLISHMENTS

**NISTIR 7368**

January 2007

U.S. DEPARTMENT OF COMMERCE

Carlos M. Gutierrez, Secretary

**Technology Administration**

Robert Cresanti, Under Secretary of Commerce for Technology

**National Institute of Standards and Technology**

William Jeffrey, Director

| Any ment    | ion of comm<br>dorsement by | ercial produ | cts is for in | formation   | only; it does | s not imply | recomme    |

|-------------|-----------------------------|--------------|---------------|-------------|---------------|-------------|------------|

| that the pr | oducts menti                | oned are ne  | cessarily th  | e best avai | lable for the | e purpose.  | aces it ii |

# **C**ONTENTS

| Welcome                                                                      | iv  |

|------------------------------------------------------------------------------|-----|

| Mission, Vision, Values, Goals                                               | vi  |

| NIST Mission                                                                 | vi  |

| Semiconductors: Backbone of the Nanoelectronics Revolution                   | vii |

| Semiconductor Electronics Division Organization                              | X   |

| Nanostructures for CD and Interconnect Metrology                             | 1   |

| Metrology for System-on-a-Chip (SoC)                                         | 8   |

| Power Semiconductor Device and Thermal Metrology                             | 12  |

| Micro-Nano-Technology (MNT)                                                  | 17  |

| Nanobiotechnology                                                            | 24  |

| Nanoelectronic Device Metrology                                              | 30  |

| Macro Electronics                                                            | 37  |

| Advanced MOS Device Reliability and Characterization                         | 42  |

| Infrastructure for Integrated Electronics Design & Manufacturing             | 46  |

| Knowledge Facilitation                                                       | 49  |

| Major Facilities / Laboratories                                              | 51  |

| National Research Council (NRC) Post-Doctoral Opportunities                  | 52  |

| SED Instrumental in New Material Data Exchange Standards                     | 57  |

| Division Leads Assessment of Measurement Needs of the Semiconductor Industry | 58  |

| Researchers Teach Nanoelectronics and Reliability Through Tutorials          | 59  |

| SED Leads Major Nanoelectronics Metrology Conference in 2007                 | 60  |

| Strong Student Outreach                                                      | 61  |

| Division Staff Recognized with Rosa and Silver Medal Awards                  | 62  |

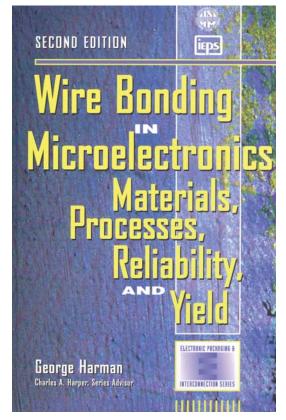

| Harman Receives IMAPS Lifetime Achievement Award                             | 63  |

| NIST's Gaithersburg, Maryland, Campus and Surrounding Area                   | 64  |

David G. Seiler, Division Chief

"Industry views SED's contributions as unique and essential to efficiently providing measurement techniques and standards."

NRC Panel Report, An Assessment of the National Institute of Standards and Technology Measurement and Standards Laboratories: Fiscal Year 2003

# WELCOME

It is my great pleasure to introduce you to the Semiconductor Electronics Division (SED) and share some of our exciting technical work. As the semiconductor industry continues its move toward silicon nanoelectronics and beyond, the introduction of new materials, efficient and reliable processing techniques, novel devices, and new metrology is essential. We have entered an era where nanotechnology is impacting our drive to smaller, faster, cheaper, and more complex chips. Innovative metrology is critical in providing solutions for long-term reliability and repeatability for these new technologies and chips. As a NIST metrologist, I welcome this opportunity to show you how the SED is helping shape the future direction of metrology for the semiconductor industry. Great opportunities exist for those of us in the metrology community to provide innovative solutions to industry's key measurement needs. I want to learn about the most important issues you are facing, as well as how improved measurements can help you innovate. Please contact us if we can be of assistance.

The primary mission of the Division is to provide the measurement and software infrastructure to U.S. industry for mainstream silicon CMOS (complementary metal-oxide semiconductor) and beyond CMOS technologies, as well as other advanced semiconductor technology needs. The Division provides necessary measurements, physical standards, and supporting data and technology; associated generic technology; software for improving interoperability; and fundamental research results to industry, government, and academia. Its programs also respond to industry measurement needs related to MicroElectroMechanical Systems (MEMS), power electronics, organic/plastic electronics, and various sub-areas of nanotechnology including nanoelectronics, nanocharacterization, nanoreliability, nanobiotechnology, and nano- and micro-fluidics.

The Division has extensive interactions with individual companies, industry organizations, professional societies, and universities; these activities enable the development of a research agenda responsive to the needs of industry and the nation. Active participation in industry roadmapping, such as the Semiconductor Industry Association's International Technology Roadmap for Semiconductors (ITRS), and standards development activities for the Semiconductor Equipment and Materials Institute (SEMI) are practiced by the Division to prioritize and establish programs with the highest potential impact. Division researchers work with SEMI on new standards to help guide the future path of our industry in areas such as MEMS, high-k dielectrics, e-diagnostics, e-manufacturing, time synchronization, traceability, and metrics. Why not become involved yourself and help shape the future direction of technology and metrology? We need innovative metrology breakthroughs that will propel our industry forward. The Division widely disseminates the results of its research, especially in the areas of standardized test methods and Standard Reference Materials (SRMs), through a variety of channels: publications, software, conferences and workshops, and participation in standards organizations and consortia.

The Division, with a staff of about 80 including full-time and part-time employees as well as guest researchers, post-doctoral associates, contractors, and students, is based in Gaithersburg, Maryland, and is one of four divisions within the Electronics and Electrical Engineering Laboratory at NIST. The Division's technical activities are organized into three groups: the Enabling Devices and ICs Group, the CMOS and Novel Devices Group, and the Electronic Information Group. The Division assists industry by providing tools such as new or improved measurement methods, SRMs, test structures and chips, standard reference data, and software that support the needed measurement infrastructure. Division personnel visit industrial sites, host a variety of visitors, and make available tutorial material on an as-needed basis. We also are active in conference and workshop activities that directly benefit the industry.

The Division, in cooperation with the National Research Council (NRC), offers competitive awards for post-doctoral research for U.S. citizens in a variety of technical fields related to the semiconductor electronics industry. For additional details, including field descriptions and qualification guidelines, please see page 52.

The technical programs, their goals, technical strategies, activities, and accomplishments described here for each Division project clearly demonstrate the impact of the SED's leadership and effective service as it continues to respond to the needs of industry and to contribute to the scientific and engineering communities. Please take an opportunity to visit our Division website, which provides further details on our Division, shows up-to-date project information, and has interactive tutorials on the Hall effect (www.eeel.nist.gov/812/hall.html) and MEMS standard test structures based on e-standards (www.eeel.nist.gov/812/test-structures/). Please also be sure visit the Systems Integration for Manufacturing Applications website (www.nist.gov/sima) on product data exchange standards.

Thank you for your interest in our Division and its technical programs! I welcome your comments and suggestions.

David H Soiler

Semiconductor Electronics Division Staff

For additional information, contact:

Division/Office Telephone: 301-975-2054 Division/Office Facsimile: 301-975-6021 On the Web: www.eeel.nist.gov/812/

# "The nature of the vision's purpose is not only to achieve a meaningful strategic or company goal, but also to build a dedicated community..."

Jay A. Conger, The Brave New World of Leadership Training, IEEE Eng. Mgmt. Review (1996)

# Mission

The **Semiconductor Electronics Division** provides technical leadership to industry, government, and academia in research and development of the semiconductor measurement and software infrastructure needs essential to the silicon microelectronics industry, advanced semiconductor materials technologies, and advanced electronic devices based upon molecular or quantum structures.

# VISION

The **Semiconductor Electronics Division** strives to be recognized as a dynamic, world-class resource for semiconductor measurements, data, models, software, and standards focused on enhancing U.S. technological competitiveness in the world market.

# **V**ALUES

The **Semiconductor Electronics Division** values its commitment to identify and meet crucial measurement technology needs. The Division values its collaboration with all segments of the semiconductor community. It strives for integrity, excellence, objectivity, responsiveness, and creativity, while maximizing and utilizing the potential of its employees.

# GOALS

The Division will:

- Aggressively pursue and achieve select metrology needs as identified in the International Technology Roadmap for Semiconductors for mainstream silicon.

- Develop new and improved process-monitoring tools, methodologies, and data for the more efficient manufacture of silicon and compound-semiconductor devices.

- Develop cooperative, multidisciplinary projects within the Division and synergistic external collaborative efforts to better meet the critical needs of the semiconductor industry.

- Support novel research that has high potential for providing breakthroughs in materials, process, devices, and measurement technologies for the semiconductor industry.

# **NIST MISSION**

NIST promotes U.S. innovation and industrial competitiveness by advancing measurement science, standards, and technology in ways that enhance economic security and improve our quality of life.

# Semiconductors: Backbone of the Nanoelectronics Revolution

The semiconductor electronics industry is vital to the U.S. economy and affects every aspect of our daily lives. Semiconductors are pervasive in the microelectronic components used in computers, MP3 players, video game consoles, HDTVs, automotive electronics, medical instrumentation, telecommunications, space technology, cell phones, and many other information technologies. Every hospital, school, factory, car, airplane, office, bank, and household contains transistors, microprocessors, and other semiconductor devices. The communications revolution, perhaps the defining social and economic transition of our time, is fueled by the invention of ever smaller, ever cheaper, ever faster chips. The explosive demands of the wireless, broadband Internet, and optical networking industries have crowned the communications chip as the dominant end market for semiconductors.

Advances in the semiconductor electronics industry are possible because of the continuing miniaturization of the transistor dimensions, which allows the construction of compact systems with tremendous computing power and memory. Miniaturization, in turn, is possible because of the perfection of fabrication techniques that allow the *integration* of circuits and thus the production of chips containing millions of elements per square centimeter. The foundation stone of this complex technology is silicon. Meeting the demands for these large-scale, complex, integrated circuits (ICs) continues to require technological advances in materials, processing, circuit design, characterization, testing, and standards.

The semiconductor electronics industry is outstripping the measurement capability needed for maintaining and improving U.S. international competitiveness. Important factors affected include product performance, price, quality, compatibility, and time to market. The Semiconductor Electronics Division provides the measurement capability needed to support the efforts of U.S. industry to improve its competitiveness. In order to support this effort, the Division also engages in technology development and fundamental research, making the findings available to industry.

The Division focuses the largest part of its resources on the development and delivery of measurement capability for two principal reasons: measurement capability has a very high impact on U.S. industry because it helps manufacturers address many of the challenges they face in realizing competitive products in the marketplace, and NIST is the official lead U.S. Government agency for measurements/metrology.

The Division focuses on developing measurement capability that is beyond the reach of the broad range of individual companies. Companies seek NIST's help for several reasons:

- The companies need NIST's special technical capability for measurement development.

- The companies need NIST's acknowledged impartiality for diagnosing a measurement problem affecting the industry broadly or for achieving adoption of a solution across the industry.

- The companies cannot develop the measurement capability needed by the industry broadly because they cannot individually capture the returns of the cost of development.

- Industry's quality standards require that key measurements be traceable to the national measurement reference standards that NIST maintains. This is a requirement of growing importance in export markets.

"The centrality of the semiconductor industry to development in the 21st century and to the continued technological preeminence of the United States cannot be exaggerated. That semiconductors have become fundamental to modern life is apparent. ... semiconductors have become the seminal technology, the vital core of an entire ecosystem that drives innovation and growth in all sectors of our economy."

> Semiconductor Industry Association (SIA) Annual Report 2006.

"NIST research in metrology is critical to reaching accuracy levels outlined in the International Technology Roadmap for Semiconductors. These measurement accuracy levels must be met to manufacture ever smaller circuits on tomorrow's semiconductor chips."

SIA applauds Congressional funding for key agencies and Focus Centers, press release, SIA, June 15, 2006. The Division interacts and collaborates with a wide variety of companies, consortia [such as Semiconductor Manufacturing Technology (SEMATECH), Semiconductor Equipment and Materials International (SEMI), and the Semiconductor Research Corporation (SRC)], academia, and other government labs to accomplish its mission. Specific details are given in the project descriptions that follow. Work in the Division results in extensive outputs or deliverables that cover knowledge and improvements in physical understanding, test methods and measurements, Standard Reference Materials (SRMs), standards, test structures and test chips, software, measurement accuracy and traceability, publications and reports, patents and Cooperative Research and Development Agreements (CRADAs), round robins, data and models, talks and short courses, company visits, conferences and workshops, consortia participation, and various activities and leadership roles on committees and working groups.

Division staff serve the semiconductor community in leadership roles on standards committees such as Semiconductor Equipment and Materials Institute (SEMI), the American Society for Testing and Materials (ASTM), and the Electronic Industries Alliance (EIA) / Joint Electron Device Engineering Council (JEDEC), societies such as IEEE, ECS, and APS, and numerous semiconductor conferences/workshops. Many test methods and standards have been developed and written over the years by NIST staff for ASTM and EIA/JEDEC, including ones for resistivity, oxygen in silicon, thin dielectrics, electromigration, and device characterization. Staff serve on various Technical Working Groups to help put together the International Technology Roadmap for Semiconductors (ITRS). These groups are Process Integration, Devices, and Structures; Assembly and Packaging; Lithography; Interconnect; Front End Processes; and RF and Analog Mixed Signal. The ITRS provides targets for equipment, material, and software suppliers; provides targets for researchers; and serves as a common reference for the semiconductor industry.

The Division also has impacted the semiconductor community by producing a number of SRMs. To date, nearly 3,000 SRMs have been sold and distributed for resistivity, oxygen in silicon, and optical thickness by ellipsometry. Hundreds of companies throughout the world have purchased these SRMs to maintain and improve their measurement capabilities.

For the future, the Division has identified nanotechnology and its various sub-areas, including nanoelectronics, nanocharacterization, nanobiotechnology, and plastic electronics, as emerging areas of research to address. There is an increasing recognition in industry that metrology is becoming more crucial for the nanotechnology era that industry has entered.

"The semiconductor industry is rapidly reaching a point in its evolution where its ability to build smaller nodes will encounter serious difficulties in the form of quantum effects and atomic level statistical fluctuations ... nanotechnology will both help keep CMOS scaling on track and enable new materials/technology platforms that satisfy market needs better than CMOS ... as current lithography methods reach their limit, the tools used in the development, manufacture, and testing of CMOS will increasingly be based on nanotechnology."

- from L. Gasman, "Why Nanotechnology Is So Important for the Semiconductor Industry," NanoMarkets White Paper, p. 2.

# INDUSTRY AND DIVISION RESEARCH DIRECTIONS NANOELECTRONICS: EXTREME CMOS AND BEYOND

Moore's law (the doubling of transistor density on integrated circuits approximately every 2 years) has provided smaller, faster, and cheaper logic and memory for over 30 years. This has been driven by the ability to continue scaling the device dimensions of the CMOS field-effect transistor (FET). Most industry analysts predict that "extreme CMOS" scaling will continue to drive the industry for at least another 10 years. However, the 15 year horizon of the International Technology Roadmap for Semiconductors (ITRS) is reaching a point which challenges the most optimistic projections for the continued scaling of CMOS. Replacing or extending CMOS with emerging devices (Beyond CMOS) is an important aspect of continuing the information revolution. These possible Beyond CMOS technologies span the realm from transistors made from silicon nanowires to devices made from nanoscale molecules.

# HETEROGENEOUS INTEGRATION AND UBIQUITOUS ELECTRONICS

The concept of multi-technology system-on-a-chip where optical, RF, MEMS and even molecular manipulation is performed on a CMOS platform to provide electronics with greater functionality is an increasingly important paradigm. The concept of ubiquitous electronics, such as organic electronics, in which electronics are cheaply incorporated in everyday items (clothes, packaging, etc.) is also an increasingly important paradigm.

# **ELECTRONIC INFORMATION**

The electronics industry is continually striving to reduce manufacturing costs in order to remain internationally competitive. More efficient design and manufacturing standards can lower the cost of manufacturing and promote open markets and a level playing field. Environmental legislation is becoming an urgent priority for the Electronics Industry. Countries are rushing to enact legislation restricting substances used in the manufacture of printed circuit boards and IC chips to promote environmental and recycling efforts. Electronics suppliers must cope with compliance with these new regulations and enact standards to be used throughout the supply chain. Outsourcing has identified the need for more widely accepted manufacturing and design standards for the printed circuit board industry, and new standards need to be developed for the Semiconductor Industry. The standardization effort must continue in order for U.S. manufacturing to remain competitive.

# **NANOBIOTECHNOLOGY**

A small but growing market already exists in the merging of semiconductor- and bio-technology. Biochips have become a focus area in biotechnology in recent years. These possibilities have not gone unnoticed by others, and major semiconductor companies and laboratories such as Agilent, Intel, Infineon, IMEC, and others have significant biotechnology research efforts underway. Our Division is working to apply micro and nanofabrication technologies to advance the state-of-the-art of single molecule measurements, single cell measurement, and DNA separations for forensic applications. Additionally, we are applying experimental and theoretical methods to advance the state-of-the art in measurements of biological and biomimetric molecules.

# SEMICONDUCTOR ELECTRONICS DIVISION ORGANIZATION

# DIVISION OFFICE (812.00)

2045

5853

| 2054 | SEILER, David G., Chief          | 2097 | HARMAN, George G.,      |

|------|----------------------------------|------|-------------------------|

| 2054 | GUARIGLIA, Lori A., OM           |      | Scientist Emeritus      |

| 4514 | COOK, Sharon W., AO              | 2050 | SECULA, Erik M.,        |

| 2079 | BENNETT, Herbert S., NIST Fellow |      | Information Specialist  |

|      |                                  | 2067 | THURBER, W. Robert (GR) |

# Enabling Devices and ICs Group (812.05)

| 2070 | GAITAN, Michael (GL) |

|------|----------------------|

| 2052 | KROFT, Terri, OM     |

# Nano-Structures for CD and Interconnect Metrology (FA)

| 2072 | CRESSWELL, Michael W. (FL) |

|------|----------------------------|

| 5026 | ALLEN, Richard A.          |

| 8193 | MURABITO, Christine E.     |

| 2234 | SCHAFFT, Harry A. (CNR)    |

| 2182 | YARIMBIYIK, Emre (GR)      |

# METROLOGY FOR SYSTEM-ON-A-CHIP (FA)

| 2071 | HEFNER, Allen R., Jr. (FL) |

|------|----------------------------|

| 5420 | AFRIDI, Muhammad Y. (CNR)  |

| 5484 | GEIST, Jon (CNR)           |

| 2236 | HOOD, Colleen E.           |

| 6018 | ORTIZ, Jose (CNR)          |

| 6757 | VARMA, Ankush (GR)         |

2071 HEENED ALL D. I. (DI.)

### POWER DEVICE AND THERMAL METROLOGY

| B.41 | NI T                       |

|------|----------------------------|

| 6018 | RIVERA-LOPEZ, Angel (CNR)  |

| 6018 | ORTIZ, Jose (CNR)          |

| 2236 | HOOD, Colleen E.           |

| 4998 | HILLKIRK, Leonardo (CNR)   |

| 8776 | HERNANDEZ, Madelaine (CNR) |

| 2081 | DUONG, Tam (CNR)           |

| 8777 | AKUFFO, Adwoa (CNR)        |

| 2071 | HEFNER, Allen R., Jr. (PL) |

# MICRO-NANO-TECHNOLOGY (MNT)

| 2070 | GAITAN, Michael (PL)       |

|------|----------------------------|

| 5026 | ALLEN, Richard A.          |

| 3095 | AUROUX, Pierre-Alain (CNR) |

| 5484 | GEIST, Jon (CNR)           |

| 4796 | HONG, Jennifer             |

| 4710 | JAHN, Andreas (GR)         |

| 2049 | MARSHALL, Janet C.         |

| 4110 | McGRAY, Craig (CNR)        |

| 6367 | MIJARES, Geraldine I.      |

|      |                            |

# MICRO-NANO-TECHNOLOGY (MNT) CONT'D

MORGAN Nicole (GR)

| 2010 | 11101101111, 1110010 (011) |

|------|----------------------------|

| 2492 | NABLO, Brian (PD)          |

| 6347 | POLK, Brian                |

| 4739 | RACIC, Milena (CNR)        |

| 5466 | REYES-HERNANDEZ, Darwin    |

| 2506 | ROBERTSON, Joey (PD)       |

| 4630 | SANKARAN, Bharat (GR)      |

| 2305 | SHAH, Jayna (GR)           |

| 2052 | STAVIS, Sam (CNR)          |

|      |                            |

KASIANOWICZ, John (PL)

### Nanobiotechnology

| 5787 | CHAN, Elaine (PD)      |

|------|------------------------|

| 4709 | HROMADA, Louis (CNR)   |

| 2492 | NABLO, Brian (PD)      |

| 4358 | REINER, Joseph (PD)    |

| 2506 | ROBERTSON, Joey (PD)   |

| 6115 | RUBINSON, Kenneth (GR) |

| 2426 | MISAKIAN, Martin (GR)  |

# WIRE BONDING TO CU/LOW-K SEMICONDUCTOR DEVICES (FA)

2097 HARMAN, George G. (FL)

# CMOS AND NOVEL DEVICES GROUP (812.06)

| 2247 | SUEHLE, John S. (GL, Acting) |

|------|------------------------------|

| 2053 | JORDAN, Melissa, OM          |

# NANOELECTRONIC DEVICE METROLOGY

| 2082 | RICHTER, Curt A. (PL)       |

|------|-----------------------------|

| 2078 | EDELSTEIN, Monica D.        |

| 8755 | GERGEL-HACKETT, Nadine (PD) |

| 2233 | HACKER, Christina           |

| 2087 | KIRILLOV, Oleg              |

| 2089 | KOPANSKI, Joseph            |

| 3241 | LI, Qiliang (CNR)           |

| 2247 | SUEHLE, John S.             |

| 3377 | WANG, Wenyong (CNR)         |

| 2088 | XIONG, Hao (CNR)            |

|      |                             |

### MACRO ELECTRONICS

- 2048 GUNDLACH, David (PL)

- 2087 KIRILLOV, Oleg

- 2089 KOPANSKI, Joseph

- 2044 NGUYEN, Nhan V.

- 2082 RICHTER, Curt A.

- 2247 SUEHLE, John S.

# ADVANCED MOS DEVICE RELIABILITY AND CHARACTERIZATION

- 2247 SUEHLE, John S. (PL)

- 2078 EDELSTEIN, Monica D.

- 8687 GURFINKEL, Moshe (CNR)

- 2044 NGUYEN, Nhan V.

- 2088 XIONG, Hao (GR)

# THEORETICAL SOLID-STATE PHYSICS FOR SEMICONDUCTORS (FA)

2079 BENNETT, Herbert S. (FL)

# ELECTRONIC INFORMATION GROUP (812.07)

3644 BRADY, Kevin G. (GL) 2053 JORDAN, Melissa, OM

# INFRASTRUCTURE FOR INTEGRATED ELECTRONICS DESIGN AND MANUFACTURING (IIEDM)

- 4284 MESSINA, John (PL)

- 8778 ARONOFF, Matthew

- 4951 BABOUD, Julien (GR)

- 5108 BERTON, Dominique (GR)

- 3644 BRADY, Kevin G.

- 2432 GRIESSER, Art

- 8581 KHALILI, Neda (S)

- 3263 KOSTICK, Jennifer A.

- 5319 LI, Ya-Shian

- 8436 MAI, Cuong (S)

- 2404 OTEMA, Eric (GR)

- 3956 SIMMON, Eric

- 5319 SMITH, Nathan (S)

## KNOWLEDGE FACILITATION

- 3263 KOSTICK, Jennifer A. (PL)

- 4229 MARIE, Mylene (S)

- 8193 MURABITO, Christine E.

### Legend:

AO = Administrative Officer

CNR = Contractor

FA = Focus Area

FL = Focus Area Leader

GL = Group Leader

GR = Guest Researcher

OM = Office Manager

PD = Post Doctoral

Appointment

PL = Project Leader

S = Student

Telephone numbers are: (301) 975-XXXX, (the four-digit extension as indicated)

# Nanostructures for CD and Interconnect Metrology

# GOALS

Contribute to a test-structure infrastructure relevant to state-of-the-art interconnect-system needs according to the International Technology Roadmap for Semiconductors (ITRS) Interconnect Report 2005, which states that the function of an interconnect system is to distribute clock and other signals and to provide power/ground to the circuits and systems functions on a chip; develop test-structure-based reference materials with emphasis on supplying traceable ITRS-compliant physical standards for critical-dimension (CD) and overlay metrology-tool calibration; and contribute to organizations supporting the development of interconnect materials and standards for CD and overlay metrology applications in the semiconductor industry.

# **CUSTOMER NEEDS**

The Semiconductor Industry Association's ITRS states that it is critically important to have suitable reference materials available when a measurement is first applied to a technology generation, especially during early development of materials and process-equipment. This project is concerned specifically with ensuring a source of such reference materials to satisfy the stated need throughout the near-term years.

Each generation of ICs is characterized by the transistor gate length whose control to specifications during IC fabrication is a primary determinant of manufacturing success. The roadmap projects the decrease of gate microprocessor unit (MPU) physical gate lengths used in state-of-the-art IC manufacturing from present levels of 28 nm to 13 nm during the near-term years. Scanning electron microscopes (SEMs) and other systems used for traditional linewidth metrology exhibit measurement uncertainties exceeding specifications for these applications. It is widely believed that potentially adverse consequences can be at least partially managed through the use of reference materials with traceable linewidths with nanometer-level uncertainties. Until now, such reference materials have been unavailable because the technology needed for their fabrication and certification has not been implemented. The technology that the project has developed for fabricating CD reference materials is known as the Single-Crystal CD Reference-Material (SCCDRM) implementation.

Interconnect technology is becoming the principal factor that determines the maximum performance that can be attained with emerging generations of integrated circuits. The dramatic reversal from performance which is limited by transistor delay, to performance which is limited by interconnect delay, challenges the approach of continuing to scale the conventional metal/dielectric system to meet future interconnect requirements. Future advances in IC performance will be governed increasingly by the advances in interconnect technology, at least as much as by advances in active devices. As aluminum is replaced by hybrid copper/barrier-metal conductors, the benefits of the higher conductivity of copper are becoming problematic as a result of the predominance of contributions of the barrier metal to the effective conductor resistance. There are two mechanisms. When barrier metal, with its higher resistivity, replaces more highly conducting copper, the proportion of the total CD, which is allocated to copper, is reduced dramatically as CD is scaled. Confounding the phenomenon, higher clock speeds favor conduction by the outer regions of the composite conductor, which render it adversely non-linear. Modeling the generalized binary-metal interconnect conductors at high frequencies is therefore a central issue. This is a very complex task on which no known reports exist in the technical literature. However, we have been able to make a start on providing a tool for dealing with this issue by drawing on NIST resources in other Divisions.

Whereas there is no simple global solution to the challenge of electrical metrology for the extracting the CDs of binary-metal interconnect conductors at this time, advances being pursued by this project are likely to play a leading role. Finally, a metrology challenge that is attributable more to scaling per se, than to the materials selected for interconnect implementation, is overlay. Overlay metrology is being challenged by exacerbation of the tool- and wafer-induced shifts that are generally manageable for technology generations introduced prior to the present time.

# TECHNICAL STRATEGY

For addressing customer needs in the interconnect arena, our four-part technical strategy builds on opportunities afforded by the project's unique SCCDRM experience. The same substrates that

**Technical Contact:** Michael W. Cresswell

**Staff-Years (FY 2006):** 1.5 professionals 0.5 guest researchers

"It is critically important to have suitable reference materials available when a measurement is first applied to a technology generation, especially during early materials-and process-equipment development"

International Technology Roadmap for Semiconductors, 2005 Edition. Available online at http://public.itrs.net/

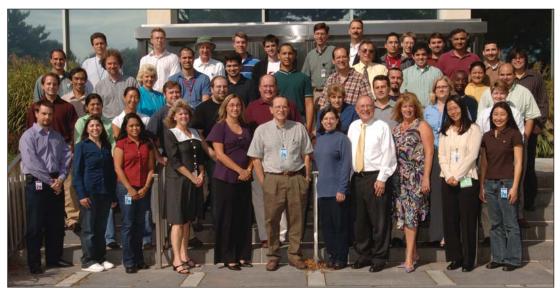

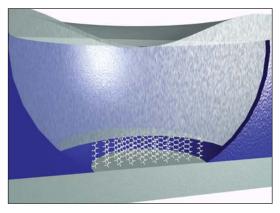

have been developed for CD reference-material applications are being applied to the fabrication of single-metal, initially copper-only, test structures with features having lateral dimensions in the 20 nm to 100 nm range. The novel process-flow, which has been reported in our joint paper with the University of Edinburgh at a recent conference, is illustrated in the figure (right). The approach shown enables a definitive assessment of the impact of feature-dimension scaling on the fundamental physics of electron transport in narrow features patterned from copper, without the complications resulting from having other metal species that serve as barrier layers. The information so provided enables modeling the performance of features that are replicated with copper-cored binary-metal technology and will aid in the verification of dimensional parameter extraction for process-control purposes.

We have initiated a study of the interaction of skin effect with high-resistance barrier metal alloys near the surfaces of conducting features at frequencies up to  $\approx 100$  GHz. This higher upper limit is driven by near-term year clock speeds having rising and falling edge components that substantially exceed 20 GHz. As mentioned above, higher clock speeds favor conduction by the outer regions of the binary-metal interconnect conductor through the so-called "skin effect" phenomenon, which renders it adversely non-linear. The technical strategy is to model the RLGC (Resistance Inductance Conductance Capacitance) parameters of a selection of binary-metal interconnect-conductor architectures over the stated range of frequencies using finite-element Maxwell software, which is available at NIST. This approach is quite ambitious, and there are no known analytical solutions for generalized binarymetal interconnect conductors. Since there is no report of such analyses in the scientific literature, we have chosen first to verify our Maxwell solutions for a selection of single-metal architectures for which analytical solutions do exist.

A class of test structures for process maintenance, where the need for innovation is driven by scaling, is overlay standards. This project has been granted a patent on an electrically calibrated test structure to serve as a process- and tool-specific overlay standard that avoids all the limitations of other approaches. The strategy is to reduce the concept to practice by replicating the test structures with a bi-level polysilicon-metal process and conduct parametrical testing.

The process flow which was devised for the fabrication of single-metal, copper-only, test structures with features having lateral dimensions in the 20 nm to 100 nm range.

Among the test structures that we are fabricating for modeling-parameter extraction are strip lines for rf-testing from DC to 40 GHz, consistent with clock speeds of road-map integrated circuits over the next several years. The strategy is the computation of rf-impedance parameters from S-parameter measurements. An important spin-off from this activity is the application of rf-measurement to validating key dimensional parameters of masks which are patterned for interconnect fabrication, another application which has been sought by the mask-vendor and mask-user industries. This work will be done initially on binary masks but, if successful, will be extended to opportunities in dimensional metrology for more complex phaseshift-mask applications. Further into the future, the experience gained here may be useful for development of a non-contact electrical-CD metrology, which is understood to be of great interest to the photo-mask industry.

The 2005 ITRS relates how both grain-size and feature dimensions affect the effective resistivity of copper in the electrical wiring of integrated circuits. The consequences are of growing concern because new technologies require ever-smaller dimensions that contribute to greater resistance and power dissipation. The project strategy is to develop an easy-to-use, versatile effective-resistivity simulation program that is superior to other approaches in use for studying size effects. It shows how the scattering of electrons by surfaces, grain boundaries, and impurities increases the effective resistivity of copper in thin films and lines as dimensions approach and become shorter than the mean free path of electrons in bulk copper. In related experi-

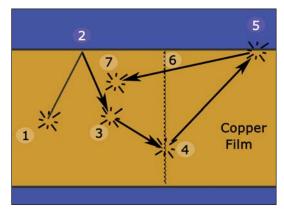

mental work, copper films are fabricated, their sheet resistances and physical thicknesses are measured, and the predictions of the simulation program are compared to experimental results. The figure below shows the various scattering events that are included in the simulation program, reported in a recent NIST news release, to simulate size effects in copper.

The scattering events that are included in the simulation program to simulate dimensional effects in copper.

The project is also providing technical support to JEDEC Committee JC14.2 of the JEDEC Solid State Technology Association on Wafer Level Reliability to enhance the reliability of copper interconnect implementations. This support is for revising interconnect standards, which were originally written for aluminum interconnects, so that they will be applicable to copper metallization. The primary focus is in writing a new JEDEC standard for constant current and temperature stress testing for electromigration, assisting in revising the JEDEC standard for isothermal stress testing for electromigration, assisting in preparing a new JEDEC stress test for stress voiding, and preparing JEDEC guidelines for designing stress-voiding test structures.

The fundamental SCCDRM reference-material strategy is to pattern SOI device layers with lattice-plane selective etches of the kind used in silicon micro machining, which provides reference features with quasi-atomically planar side-walls. This unique attribute is highly desirable for the intended applications, particularly if the quasi-atomically planar sidewall smoothness can be further extended to reference-feature segment lengths of up to 2  $\mu$ m. Essential elements of the implementation include both bulk and SOI (Silicon on Insulator) starting silicon wafers having a (110) orientation; alignment of the reference features to specific lattice vectors; and lithographic patterning with lattice-plane selective

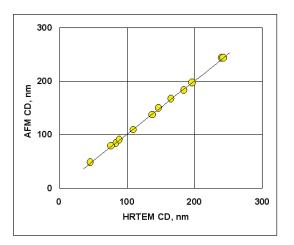

etches of the kind used in silicon micro-machining. However, the difficulty of obtaining satisfactory SOI material in larger diameters is driving us towards a bulk-wafer starting-material strategy. The roadmap states that measurement and certification of reference materials must be carried out using standardized or well-documented test procedures. The traceability path for dimensional certification of the project's SCCDRMs is responsive to this requirement and makes measurements of a selection of reference-feature CDs on multiple chips with both Atomic-Force Microscopy (AFM) and high-resolution transmission electron microscopy (HRTEM) imaging. The former technique is highly repeatable and of manageable cost while the latter enables a lattice-plane count that allows expression of each CD in terms of a traceable distance, which is the periodicity of silicon (111) lattice planes. However, HRTEM is totally destructive and thus is not useful for supplying reference features to end users. The project's traceability strategy thus features state-of-the-art AFM as a transfer metrology to deal with this constraint. Transfer metrology relates CDs extracted by, in this case, AFM to be traced to SI units through the construction of a so-called calibration curve. An example of such a curve is shown in the figure below.

Transfer metrology relates CDs extracted by AFM to be traced to values SI units through the construction of a so-called calibration curve.

To maintain the maximum possible accuracy in the transfer-metrology operation, an elaborate reference-feature selection protocol has been established to identify reference features that qualify by virtue of their CD-uniformity, as contributors to the construction of the calibration curve, or for delivery to end users. Multiple reference features on a large set of as-patterned test chips are identified initially

by high-power optical inspection. This procedure checks primarily for continuity, cosmetics, and apparent uniformity of the narrowest-drawn of sets of six features that are incorporated into test structures, which are called HRTEM targets. Drawn feature linewidths range from 350 nm to 600 nm, and the "process bias" typically decreases these to etched CDs of between 50 nm and 300 nm. The "best" 10 % of the AFM targets passing optical inspection, and having estimated replicated CDs in the range 50 nm to 200 nm, are then SEM-imaged at 20KX to narrow the selection process further. Digitized profiles of the CDs of top-down SEM images are then extracted at 25 nm intervals. The measurements are transferred to a database, which is then interrogated to identify chips, and the AFM targets on them, that have more uniform SEM-CD profiles at the narrower CDs - typically less than 150 nm. Candidate AFM targets so identified on each chip are then CD-profiled by AFM. Chips having AFM targets with all six features having superior uniformity are then partitioned into a calibration sub-set and a product subset. All six features of the selected targets on the chips on the calibration sub-set are then subjected to HRTEM imaging. These are the chips whose designated AFM targets are to be used as contributors to the calibration curve. The design of all HRTEM targets enables the capture of six HRTEM images in a single dual-beam FIB-and-thinning operation. Since such operations are very costly, this capability is economically advantageous. Moreover, since the features on each target are designed such that they are systematically staggered in CD by increments of 30 nm, HRTEM inspection of a single target enables the generation of a 6-point calibration curve spanning a 150 nm range.

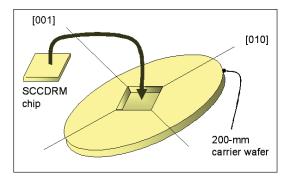

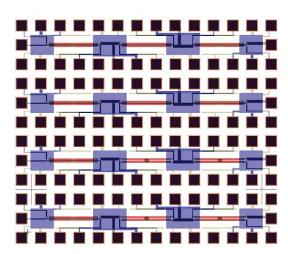

Since 200 mm (110) starting material, which is preferred by end-users in industry, is unobtainable at an acceptable cost, this project's technical strategy has been to dice each 150 mm (110) wafer after lithography and to mount the separate chips in micro-machined standard 200 mm carrier wafers to accommodate the product reference-feature chips. The scheme is shown in the figure (right). The result is that finished units are rendered metrologytool-compatible at an acceptable cost.

The project's technical strategy in reference materials is now evolving in the ways listed below. In summary, it is responding to industry push to implement measures that make the SCCDRMs more compatible with end-user requirements. These activities include:

- replacing the carrier-wafer with a monolithic

200 mm wafer implementation

- replacing the buried oxide of SOI wafers with a buried boron diffusion having an epitaxial silicon layer deposited over it

- further reducing the CDs of calibrated features to 20 nm and the uncertainties of the calibrated CD to less than 1.0 nm through systematic process-refinement experiments

- improving the reference feature's CD uniformity to enable certifying the CD of an extended length

- improving on-wafer navigation for the end user convenience

- calibrating a selection of optical-CD (OCD) gratings that are replicated at the same time as the isolated lines that have been supplied so far

- improving management of the organic residues that sometimes impair the cosmetic appearance of the reference features and their environment on the wafer and to some extent adversely affect the uncertainty values of the delivered product

- exploring the potential of OCD gratings patterned with SCCDRM technology to assess the uncertainty and usefulness of this implementation

- conducting extensive studies of the wafer processing and identifying which process parameters provide superior cross-section uniformity and narrowness

The technical strategy has been to dice each 150 mm (110) wafer after lithography and to mount selected chips in micro-machined standard 200 mm carrier wafers to accommodate the product reference-feature chips.

Implementing these aggressive measures requires wafer-processing facilities that require innovative teaming with other laboratories. Our strategy takes a page from the roadmap that explicitly states that standards institutions need rapid access to state of the art development and manufacturing capability to fabricate relevant reference materials. Likewise, the roadmap states that metrology, process, and standards research institutes, standards organizations, metrology tool suppliers, and the university community should continue to cooperate on standardization and improvement of methods and on production of reference materials.

**DELIVERABLE:** Report results of modeling the distributed resistance and capacitance values of interconnect conductors that can be simulated by both analytical solutions and a commercial Maxwell solver.

**DELIVERABLE:** Fabricate and test chemically stable test structures having copper-only features and make electrical-CD (ECD) measurements.

**DELIVERABLE:** Report initial electrical measurements made on second-generation SCCDRM test structures that have been converted to single-crystal nickel-silicide.

**DELIVERABLE:** Design, model, fabricate, and test a selection of co-planar waveguide test structures on chrome-on-glass photo-masks to evaluate the efficacy of developing a non-contact ECD method for sampling printed features.

**DELIVERABLE:** Conclude and report on the screening experiment to identify which combinations of six pattern-transfer process factors drive down reference feature CDs and their uncertainties.

**DELIVERABLE:** Fabricate and conduct AFM metrology of trenches patterned into (110) SOI device layers for their evaluation as micro fluidic channels for MEMS-based bio-applications.

**DELIVERABLE:** Devise and demonstrate a hybrid optical-e-beam-direct-write lithography-process to pattern of a selection 100 mm or 200 mm bulk-silicon (110) wafers with SCCDRM test structures with CDs at or below the 20 nm level.

**DELIVERABLE:** Design a test chip for, and apply 193 nm lithography to the patterning of, a selection of 200 mm bulk-silicon (110) wafers with SCCDRM test structures having reference-feature CDs at or below the 20 nm level.

**DELIVERABLE:** Extend tests and analyses for the evaluation SEM-CD measurements as a SCCDRM transfer metrology.

**DELIVERABLE:** Fabricate and SEM-inspect a large selection of OCD grids patterned on SCCDRM wafers as an OCD reference material.

**DELIVERABLE:** Initiate the implementation of a plan to fabricate and calibrate a selection of isolated-line CD-SRMs.

# **A**CCOMPLISHMENTS

- This project, in collaboration the NIST Precision Engineering and Statistical Engineering Divisions, has recently designed and implemented a screening experiment to identify which combinations of six pattern-transfer process factors drive down SCCDRM (Single-Crystal CD Reference-Material) reference-feature CDs and their uncertainties. Initial results include CD reductions to 25 nm with superior uniformities.

- SCCDRM chip layouts have been designed for three new fabrication ventures featuring 200 mm wafer monolithic implementations. One of these is for a new hybrid optical/e-beam-direct-write process designed to reduce CDs to below 20 nm. Another is to take advantage of an offer by SEMATECH to collaborate on the fabrication of a new generation of SCCDRMs using state-of-the-art 193 nm lithography. The third is to respond to an interest expressed by other NIST operating units to sponsor a joint SRM venture.

- Our SCCDRM implementation is well suited to the fabrication of calibrated reference materials for the emerging metrology known as optical-CD (OCD). We have now accomplished the first-ever fabrication and extensive inspection by SEM of gratings suitable for this purpose.

- A paper that describes a new simulation program and its use to study the effects of surface and grain-boundary scattering on the effective resistivity of copper in thin planar films and small cross-section lines was completed. The paper was published by the Microelectronics Reliability journal in July 2006.

- Project staff completed for publication a new JEDEC standard for electro-migration stress testing with constant current and temperature.

- Project staff prepared a comprehensive manuscript on second-generation SCCDRM reference-materials for publication as the lead article in the May-June 2006 issue of the NIST Journal of Research.

- As a result of close extended collaboration with the University of Edinburgh, the project has been able to develop and report a unique copper damascene process for the fabrication of a scaled electrical-CD test structure having copper-only features. The purpose is to facilitate studies of electron transport in pure copper without having to correct for the complexities of the interaction of copper with barrier-metal films. This implementation enables the separation of the effects of surface

"A great team effort.

Quality is high to be able to achieve multiple

(6) linewidth standards certified to about a 1 nm uncertainty."

IBM response to 2006 survey sent by the Office of Microelectronics Programs.

"The semiconductor fabrication engineer who is responsible for metrology perennially struggles to determine whether his tool be it an atomic force microscope (AFM), SEM or anything else - is properly calibrated. This requires a highly dependable, traceable linewidth standard, which is something that is not always easily available."

> A. Braun, Linewidth Standard to Calibrate AFMs, SEMs and OCD Tools, Semiconductor International, August 1, 2006.

- and grain-boundary scattering, as a function of the cross-section dimensions of the conductor by electrical testing. Our joint paper describing the accomplishment was presented at the ICMTS 2006 conference in Austin, Texas, on March 8, 2006.

- In close collaboration with the Laboratory for Interconnect and Packaging at the University of Texas at Austin, test structures for the investigation of the effect of linewidth scaling on electron transport in nickel mono-silicide features have been designed and fabricated. The features were patterned on (110) silicon-on-insulator wafers with i-line lithography that replicated test structures from which voltage/current (V/I) measurements could be extracted. Subsequently, the patterning of single-crystal features with direct-write electronbeam lithography has been developed in order to facilitate future reduction of the linewidths of NiSi features, which have a highly controlled surface microstructure, to linewidths below 40 nm. Our joint paper illustrating these results was also presented at the ICMTS 2006 conference in Austin, Texas, on March 8, 2006.

- Work has continued on a new CD metrology based on coplanar waveguide test structures. Extensive e-m field modeling of characteristic impedance and distributed capacitance, which we have conducted in collaboration with the Department of Electrical and Computer Engineering at George Washington University, indicates that the extraction of these values from S-parameter measurements can be applied to sampling CDs of test-structure features that are printed on photomasks. At this time, the design of a set of thru and de-embedding structures has been designed, and a supplier of the substrate has been identified. Our joint abstract on the results has been accepted for presentation at the SPIE Bay Area Chrome-Users Symposium in September 2006. It now seems possible that coplanar waveguide test structures may provide a means of extracting electrical and dimensional information of copper interconnect features fabricated with barrier-metal coatings.

- A new JEDEC standard, JESD202, was completed and published in March 2006. The standard describes an accelerated stress test method for determining sample estimates and their confidence limits of the median-time-to-failure, sigma, and early percentile of a log-normal distribution, which are used to characterize the electromigration failure-time distribution of equivalent metal lines subjected to a constant current-density and temperature stress. Procedures are provided to analyze complete and singly, right-censored failure-time data.

- The computer-aided design (CAD) of a new test chip for the fabrication of test structures that can be electrically calibrated to serve as an overlay reference material for high-density interconnect fabrication has been completed. A program to simulate and validate the calibration of the standard has been applied to the design, and the fabrication of a wafer-lot has been initiated.

- In collaboration with NIST operations in Boulder, Colorado, we applied Maxwell software to the calculation of RLGC parameters of cylindrical copper conductors with diameters ranging from 50 nm to 5000 nm, which were coated with TaN barrier metal of thicknesses typical of state-of-theart IC-interconnect applications. At frequencies above 10 GHz, significant increases in resistance were observed as a consequence of the skineffect induced amplification of transmission losses caused by barrier-metal coatings. A selection of these results have now been compared with those obtained for copper-only wires that were obtained from exact solutions of Maxwell-based Bessel equations. Initial results indicate close comparisons for the cases that have so far been compared.

# **FY OUTPUTS**

### **C**OLLABORATIONS

We are interacting with the staff of the ISMI Subsidiary of SEMATECH, who have invited us to share space on their new "CMAG6" reticle for their SVGL 193 nm Step-and-Scan lithography tool to fabricate an advanced generation of SCCDRMs for distribution to the member companies, as well as for possible calibration and distribution from NIST as SRMs. Our most-recently initiated joint activity is automated SEM image analysis for calibrating OCD gratings.

The Scottish Microelectronics Centre at the University of Edinburgh (SMC) is continuing to work with us on a selection of the project's wafer-fabrication needs, especially i-line lithography and damascene-copper processing. This collaboration continues to generate multiple joint publications.

Our collaboration with two senior professors and their graduate students at the Electrical Engineering and Computer Sciences Department at George Washington University contributes special expertise in rf test-structure design, microwave parameter extraction from network-analyzer measurements, and the physics of modeling electron transport in metallic nanostructures.

We interact very regularly and closely with NIST's MEL, Physics, and ITL Laboratories. We share an ongoing intramural ATP program to reduce the certified CDs and uncertainties of SCCDRMs through fabrication refinements with ITL and MEL.

A new collaboration with the Microelectronics Research Center Department at the University of Texas at Austin has resulted in the transformation of narrow SCCDRM features to silicide material. They are also contributing very desirable ultra-narrow-line lithography for our next-generation SCCDRM fabrication.

## STANDARDS COMMITTEE PARTICIPATION

Electrical Test Structures Task Force, Co-chair (Richard A. Allen)

SEMI International Standards Micro-lithography Committee, member (Richard A. Allen)

JEDEC JESD33B standards (Harry A. Schafft)

### PRESS RELEASE

"NIST Unveils Atom-based Standards for Measuring Chip Features Under 50 Nanometers," NIST News Release, February 24, 2005.

## RECENT PUBLICATIONS

- E. Yarimbiyik, H. A. Scahfft, R. A. Allen, M. E. Zaghloul, "Modeling and Simulation of Nanometer Scale Copper Resistivity," IEEE Device and Materials Reliability, Vol. 46, No. 7, pp. 1050-1057 (01-JUL-2006)

- E. Yarimbiyik, H. A. Schafft, R. A. Allen, M. Zahgoul, D. L. Blackburn, "Implementation of Simulation Program for Modeling the Effective Resistivity of Nanometer Scale Film and Line Interconnects," NIST Interagency/Internal Report (NISTIR) 7234, (01-FEB-2006)

- R. G. Dixson, R. A. Allen, W. F. Guthrie, M. W. Cresswell, "Traceable Calibration of Critical-dimension Atomic Force Microscope Linewidth Measurements with Nanometer Uncertainty," J. Vacuum Sci. Technol. B, Vol. 23, No. 6, pp. 3028-3032 (30-NOV-2005)

- M. W. Cresswell, R. G. Dixson, W. F. Guthrie, R. A. Allen, C. E. Murabito, B. Park, J. V. Martinez, A. Hunt, "Critical Dimension Reference Features with Sub-Five Nanometer Uncertainty," SPIE 30th International Symposium Micro-lithography, Metrology, Inspection, and Process Control, Feb 27, 2005 to Mar 04, 2005, San Jose, California, Vol. 5752, pp. 288-303 (30-MAY-2005)

- R. A. Allen, A. Hunt, C. E. Murabito, B. Park, W. F. Guthrie, M. W. Cresswell, "Extraction of Critical Dimension Reference Feature CDs from New Test Structure Using HRTEM Imaging," ICMTS IEEE International Conference on Micro-electronic Test Structures, Apr 04-07, 2005, Leuven, Belgium, 6 pp. (18-APR-2005)

- M. W. Cresswell, B. Park, R. A. Allen, W. F. Guthrie, R. G. Dixson, W. Tan, C. E. Murabito, "Comparison of SEM and HRTEM CD-Measurements Extracted from Monocrystalline Test-Structures Having Feature Linewidths from 40 nm to 240 nm," ICMTS 2005 International Conference on Microelectronic Test Structures, Apr 04-07, 2005, Leuven, Belgium, Select State, 6 pp. (18-APR-2005)

- M. W. Cresswell, R. A. Allen, R. G. Dixson, W. F. Guthrie, C. E. Murabito, B. Park, J. V. Martinez, "Report of Investigation of RM 8111: Single-Crystal Critical Dimension Prototype Reference Materials," (02-MAR-2005)

# METROLOGY FOR SYSTEM-ON-A-CHIP (SoC)

# **Technical Contact:**

A. R. Hefner, Jr. M. Y. Afridi

# Staff-Years (FY 2006):

1 professional 1.75 guest researchers 0.5 students

"... the trend toward digitisation notwithstanding, the analogue content of SOCs is likely to increase."

> Ron Wilson, Electronic Design News (EDN), 2006

### GOALS

One of the key metrology issues confronting the semiconductor System-on-a-Chip (SoC) industry is the development of measurement methods and standards for characterizing embedded-sensor (ES) Virtual Components (ES-VCs), a critical class of building blocks from which SoCs are developed. The goal of this project is to promote and support the development of hardware and software standards for specifying ES-VCs compatible with the SoC integration methodology used for digital IC design. This goal has been extended to include SoC compatibility with the IEEE 1451 series of sensor communication network standards at the request of one of the project sponsors.

This NIST effort will enable ES-VCs to be included in SoC computer-aided design (CAD) libraries and enable integration of ES-VCs with the existing digital VCs used ubiquitously by industry to design large ICs. The methods and standards developed as a result of this work will be essential for the realization of integrated, low-cost, smart homeland security and environmental sensor systems. One focus is on delivering standards to facilitate the incorporation of multi-technology (MT) VCs including MEMS (Micro-Electro-Mechanical Systems)-based VCs into SoCs.

The project activities include the development of: multi-technology hardware description language (HDL) models, VC interface standards, synthesis and scaling standards for ES-VCs compatible with digital methodologies, testing standards, verification standards, and high-level models of system components. The NIST MEMS-based integrated gas-sensing VC is used as a test bed to demonstrate the viability of these standards. In addition, the demonstration of general purpose gas-sensing VC methodologies is used to facilitate the adoption of these MT-VCs into new Homeland Security and industrial applications.

# **CUSTOMER NEEDS**

Recent advances in high density CMOS integration and the ability to co-integrate MEMS-based sensor devices enable cost effective complex system designs fabricated on a single chip. The need for standards arises when the SoC is designed using IP (Intellectual Property) cores from multiple vendors. These cores must be compatible for design success, thus demanding standards in the area of

interoperable interfaces, models, and verification strategies for multi-technology SoC designs.

The SoC design challenges include managing increasing system complexity, achieving system-level verification, and bridging the separate disciplines of system architecture and chip design. These challenges are being overcome with the use of platform-based design approaches that emphasize design reuse; *i.e.*, the development of ES-VCs that can be used as cost-effective building blocks for SoC devices and standards for ES-VC IP interoperability with the SoC design flow.

One set of customers for this infrastructure building will be the makers of system design software, ES-SoC IP designers, SoC manufacturers, and systems designers. This is generally recognized by the chip designers, manufacturers, and electronic design automation (EDA) tool developers:

- "What is the most recent development that promises to truly enable a system on a chip? It is the ability to combine CMOS and MEMS structures into one process flow."

- Randy Frank and Dave Zehrbach, Motorola, in *Sensors Online*

- -"Definitely, System-on-a-chip is the driving paradigm in our space, and there are some fundamental differences in culture and engineering mentality as well as some new technical skills that need to be developed in engineering. At the highest level, system-on-a-chip implies that you need to think like a system designer but implement like a chip designer, and those traditionally have been different disciplines..."

- Shane Robison, Executive Vice President of Engineering, Cadence Design Systems, Inc., EDAcafe.com

Another set of customers for ES-VC SoCs are the ultimate users of these chips. Compatibility with existing and emerging sensor communication standards such as IEEE 1451 will be essential so that the SoCs can be utilized in law enforcement and homeland security applications.

### TECHNICAL STRATEGY

To successfully develop ES-VCs for SoC design methodology, the first step in this multi-step process is to develop the ability to make the ES-VC devices via a standard CMOS compatible process. To exercise this capability we have chosen a MEMS microhotplate-based embedded gas-sensor,

including operational amplifiers, decoders, and an analog-to-digital converter (ADC), and a microcontroller for control and data processing.

The second step is to make ES-VCs compatible with the standard digital SoC design methodology. This approach will require ES-VC to incorporate digital interface circuitry and to have the DFT/BIST (Design For Test/Built-In Self Test) functionality required by SoC standards. To facilitate this approach we will develop methodologies and standards for adding digital shells to ES-VCs and demonstrate them on the gas-sensor VC described above.

**DELIVERABLE:** Develop and fabricate a fully digital gas-sensor VC in a standard CMOS 0.5 μm technology to demonstrate a standard digital interface and SoC Design-For-Test functionality.

The predominant design approach used by industry for SoC devices is top-down design. This requires that high-level models (in SystemC/HDL) exist for the VCs that are candidates for use in any particular system of interest. Compared to those for digital VCs, the methodology and standards for developing high-level models for ES-VCs are at best poorly developed. To address this need, high-level models are being developed for ES-VCs using Analog and Digital Hardware Description Languages and higher-level system description languages such as SystemC. We are also developing methodologies to validate these models. The digital systems industry has standards set by organizations such as OCP-IP, VSIA, and OSCI to foster large-scale interchange and interoperability of modular digital IP, and we believe that such standards in the ES-VC field are a key factor for the growth of an ES-VC IP industry.

**DELIVERABLE:** Compare high-level model simulation results for microhotplate-based gas-sensor ES-VCs with measured data from a fully digital ES-VC.

The synthesis process is well defined for the digital SoC design and is well supported by a large number of design libraries. Currently the libraries, methodology, and standards for ES-VC synthesis do not exist. We are developing standards and metrologies for ES-VCs that will be compatible with standard digital synthesis tools.

**DELIVERABLE:** Synthesize and fabricate a microcontroller IP core with an IEEE 1451 compatible interface in a standard 0.25 μm CMOS process VC.

**DELIVERABLE:** Develop methodology and standards to allow ES-VC to be synthesized by standard MT-synthesis tools and demonstrate their viability via our microhotplate gas-sensor VC.

Scaling digital circuitry is a key capability used by digital designers to reduce costs and ensure compatibility with different fabrication technologies. Since most systems that would use ES-VCs will be predominantly digital, it is important that there be an equivalent scaling capability for the ES-VCs. To address the need for scaling ES-VCs, we are developing metrologies for digital-compatible scaling processes.

**DELIVERABLE:** Develop methodologies and standards for an equivalent ES-VC scaling approach and demonstrate its viability via our microhotplate gassensor technology.

The testability of ES-VCs represents another significant challenge since standards and methodologies for non-digital circuits do not exist. The most promising approach to address testability is to use BIST techniques. To facilitate this approach, we will develop methodologies and standards for adding BIST to ES-VCs and interface with them via the digital shell.

**DELIVERABLE:** Develop methodologies for built-in self test of ES-VC devices and demonstrate their viability via our microhotplate gas-sensor technology.

NIST is a natural home for this work because NIST has advanced measurement capabilities across the spectrum of sensor technologies.

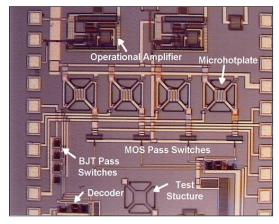

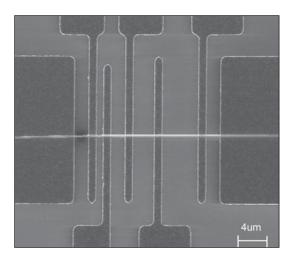

Micrograph of gas-sensor system to be used as demonstration vehicle.

### **ACCOMPLISHMENTS**

- Investigated existing and emerging SoC design methodologies and adapted digital SoC design tool-flow to enable integration of mixed-signal MEMS VCs.

- A four element gas-sensor VC was successfully designed, fabricated, and electrically characterized to demonstrate that the design approach

was compatible with SoC design methodology. The performance of the 8-bit analog-to-digital converter (ADC) exceeded the gas-sensor VC design requirements.

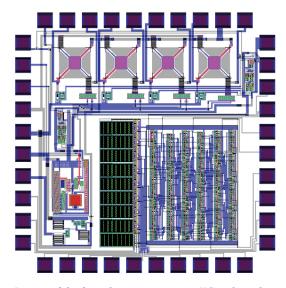

Layout of the four element gas-sensor VC with analogto-digital control.

■ Electrostatic discharge (ESD) protection structures were added to the gas-sensor and successfully tested. These ESD test structures are based on multi-finger thyristor-type devices and are designed to achieve optimum performance and reduced area.

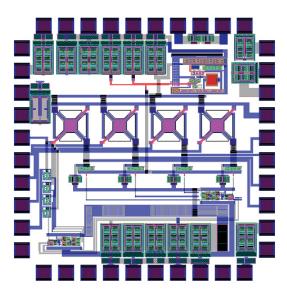

Layout of the four element gas-sensor VC with electrostatic discharge (EDS) protection circuitry.

■ A new post-process etching technique was developed to integrate MEMS devices with standard submicron CMOS processes and a new microhotplate design that scales with standard CMOS structures and voltage levels. This will enable co-integration of MEMS sensor devices with high density submicron digital systems using cost effective standard CMOS foundries. The submicron gas-sensor test chip was characterized. Characterization data showed the new scalable microhotplate will provide the temperature required for gas-sensor operation at 3.3 V.

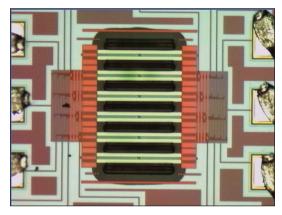

New microhotplate design implemented in standard submicron CMOS technology.

- Methodologies for designing digital interface shell functionality for ES-VCs were developed and demonstrated by designing the gas sensor SoC architecture.

- A high-level model of the microhotplate gas sensor ES-VC was developed. A HDL-based microcontroller core was synthesized for a 0.25 µm standard CMOS fabrication process. High-speed SystemC models of the microcontroller and microhotplate were developed to facilitate SoC software design and protocol development. This is the first time a MEMS device has been modeled in SystemC, and the results demonstrated the importance of including MEMS-device models in high level system modeling

- Microhotplate-based gas-sensor yield was improved by adopting a new chromium etchant.

- A computer-controlled gas-delivery system was designed, assembled, and tested. The gas delivery protocols for calibrating the microhotplate-based gas sensors were designed and implemented.

- A submicron-microhotplate test-structure chip was designed to compare the performance of different CMOS compatible temperature sensors and

to measure the contact resistance between different types of post-processed gas sensor electrodes. This chip also supports the extraction of more accurate microhotplate thermal-model parameters.

Layout of new microhotplate test-structure chip with different types of temperature sensors and four point electrodes for gas-sensor film contact-resistance studies.

## **FY OUTPUTS**

### RECOGNITION

2005 George Abraham Outstanding Paper Award:

Y. Afridi, A. Hefner, C. Ellenwood, R. Cavicchi, and S. Semancik "Characterization System for Embedded Gas-sensor Systems-on-a-Chip," GOMACTECH 2005, pp. 94-97, 2005.

# RECENT PUBLICATIONS

- J. Salcedo, J. J. Liou, M. Y. Afridi, A. R. Hefner Jr., "On-Chip Electrostatic Discharge Protection for CMOS Gas Sensor Systems-on-a-Chip (SoC)," IEEE J. Solid State Circuits, Vol. 46, No. 8, pp. 1285-1294 (01-AUG-2006)

- J. Geist, M. Y. Afridi, A. Varma, A. R. Hefner Jr., "Simple Thermal Efficiency Model for CMOS-Microhotplate Design," Journal of Research (NIST JRES), Vol. 111, No. 3, pp. 243-253 (31-MAY-2006)

- M. Y. Afridi, A. R. Hefner Jr., C. H. Hood, R. E. Cavicchi, S. Semancik, "Characterization System for Embedded Gas Sensor Systems-on-a-Chip," GOMAC Digest of Technical Papers, GOMACTech, Apr 04-07, 2005, Las Vegas, Nevada, pp. 94-97 (01-DEC-2005)

- M. Y. Afridi, A. R. Hefner Jr., J. Geist, C. E. Hood, A. Varma, B. Jacob, "Microhotplate-Based Sensor Platform for Submicron SoC Designs," 2005 International Semiconductor Device Research Symposium, Dec 07-09, 2005, Bethesda, Maryland, pp. 260-261 (09-DEC-2005)

- J. A. Salcedo, J. J. Liou, M. Y. Afridi, A. R. Hefner Jr., "Novel Electrostatic Discharge Protection Structure for a Monolithic Gas Sensor Systems-On-A-Chip," Proc., Conference Proceedings IEEE International Symposium on Circuits and Systems, IEEE International Symposium on Circuits and Systems, May 23-26, 2005, Kobe, Japan, (01-MAR-2005)

# Power Semiconductor Device and Thermal Metrology

**Technical Contact:** A. R. Hefner, Jr.

Staff-Years (FY 2006):

- 1.0 professional

- 4.8 contractors

"In 2002, Dr. Calvin Carter of Cree Inc. received the US National Medal of Technology from President George W. Bush for: "his exceptional contributions to the development of Silicon Carbide wafers, leading to new industries in wide band-gap semiconductors and enabling other new industries in ... more efficient/ compact power supplies, and higher efficiency power distribution/transmission systems."

### GOALS

The goals of the project are to (1) develop electrical and thermal measurement methods and equipment in support of the development and application of advanced power semiconductor devices and (2) develop advanced thermal measurements methods and standards for characterizing integrated circuits (ICs) and devices.

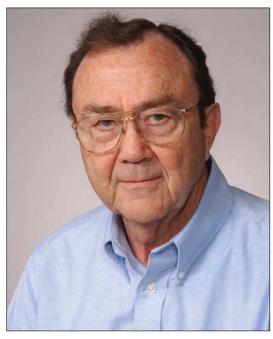

Allen Hefner, Jr., performs high-speed, high-voltage silicon carbide device characterization using NIST-developed, specialized equipment. Copyright Robert Rathe

# **CUSTOMER NEEDS**

The electronics industry faces significant technical challenges in developing more thermally efficient ICs and power semiconductor devices. Power consumption and heat removal within IC devices are becoming critically important as expressed in the 2005 ITRS: "Power consumption is now the major technical problem facing the semiconductor industry. As feature sizes shrink below 0.1 micron, static power is posing new low-power design challenges." The need for efficient power semiconductor devices stems from a range of application requirements including more efficient switch-mode power supplies for computers and consumer appliances, to motor drives for electric automobile and higher power traction applications, and finally to more efficient power generation, transmission, and distribution.

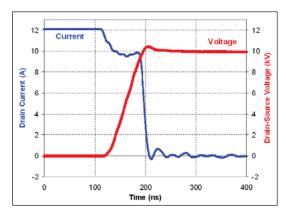

Recent advances in single crystal SiC material and fabrication technology have ushered in a new era of wide band-gap power semiconductor devices. This has led to the commercialization of SiC power Schottky diode products in the 400 V to 1200 V range and to the development of High-Voltage, High-Frequency (HV-HF) power devices with 10 kV, 20 kHz power switching capability. The emergence of HV-HF devices with such capability is expected to revolutionize power distribution and conversion by extending the use of switch-mode power conversion technology to high voltage applications. With the introduction of this new SiC power device technology comes new requirements for metrology and standards that are being addressed by NIST.

NIST is playing a lead role in industry and government programs to accelerate the development and application insertion of SiC power devices. The Defense Advanced Research Projects Agency (DARPA) Wide-Band-gap Semiconductor Technology High Power Electronics Program (WBST-HPE) is developing power semiconductor modules with 15 kV, 110 A, 20 kHz switching capability. The recently announced WBST-HPE Phase 3 effort (www.darpa.mil/baa/baa06-30.html) anticipates that this semiconductor technology will enable the HV-HF switching required for a Solid State Power Substation (SSPS) in future Naval aircraft carriers. The Electric Power Research Institute (EPRI) seeks to utilize SiC power devices for advanced distribution automation using solid-state distribution transformers. The Department of Energy has also recently identified HV-HF power devices as an enabling technology for future alternative energy sources and power plants.

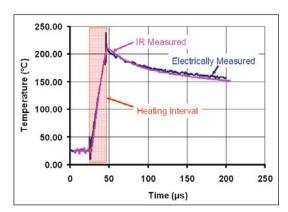

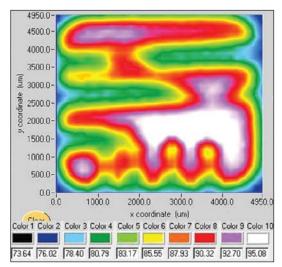

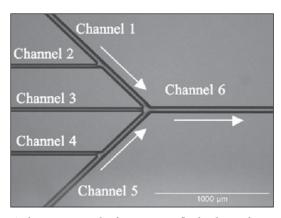

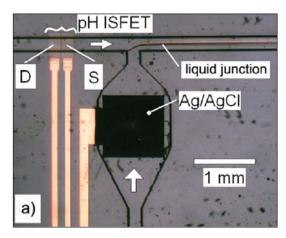

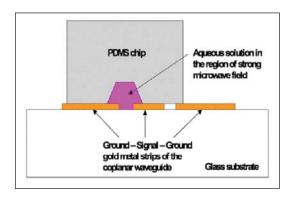

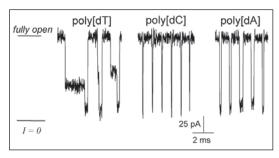

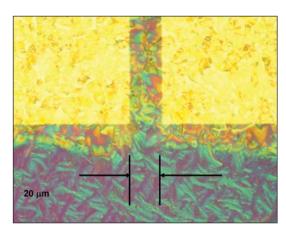

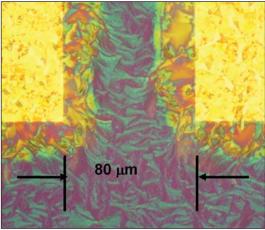

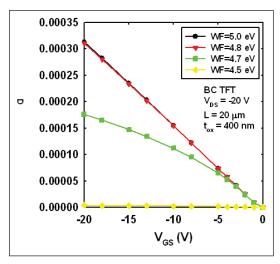

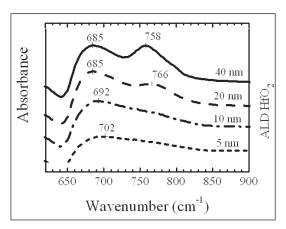

While overcoming thermal limitations has always been at the forefront of power semiconductor technology, this has only recently become a critical issue for IC devices. The major issues include: (1) power levels in CPUs have reached the same levels as in power devices; (2) high-performance IC Functional Unit Blocks (FUBs) are leading to non-uniform dynamic heating of IC chips; and (3) shrinking dimensions and increasing operating frequencies of ICs are causing significant power dissipation in the interconnects. The ITRS 2005 states that "there is strong need to establish industry wide transient thermal measurement technique standard." NIST is addressing these